Quantum Dot DBR Lasers Monolithically Integrated on Silicon Photonics by In-Pocket Heteroepitaxy

By Rosalyn Koscica 1, Alec Skipper 1, Bei Shi 1, Kaiyin Feng 1, Gerald Leake 2 and Michael Zylstra 3

1 University of California, USA

2 RF SUNY Polytechnic Institute, USA

3 Analog Photonics, USA

Abstract:

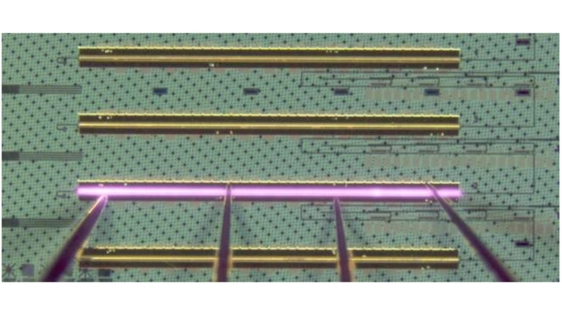

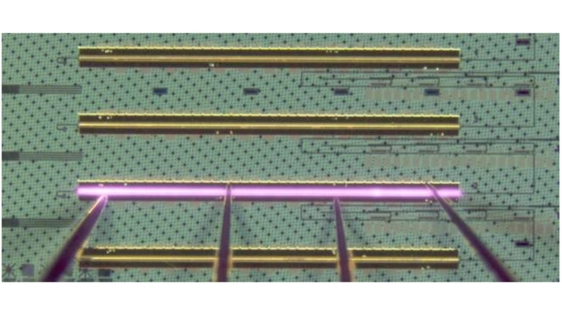

Monolithically integrated lasers on silicon photonics enable scalable, foundry-compatible production for data communications applications. However, material mismatches in heteroepitaxial systems and high coupling losses pose challenges for III-V integration on silicon. We combine three techniques: recessed silicon pockets for III-V growth, two-step heteroepitaxy using both MOCVD and MBE, and a polymer facet gap-fill approach to develop O-band InAs quantum dot lasers monolithically integrated on silicon photonics chiplets. Lasers coupled to silicon ring resonators and silicon nitride distributed Bragg reflectors (DBR) demonstrate single-mode lasing with side-mode suppression ratio up to 32 dB. Devices lase at temperatures up to 105 °C with an extrapolated operational lifetime of 6.2 years at 35 °C.

Monolithically integrated lasers on silicon photonics enable scalable, foundry-compatible production for data communications applications. However, material mismatches in heteroepitaxial systems and high coupling losses pose challenges for III-V integration on silicon. We combine three techniques: recessed silicon pockets for III-V growth, two-step heteroepitaxy using both MOCVD and MBE, and a polymer facet gap-fill approach to develop O-band InAs quantum dot lasers monolithically integrated on silicon photonics chiplets. Lasers coupled to silicon ring resonators and silicon nitride distributed Bragg reflectors (DBR) demonstrate single-mode lasing with side-mode suppression ratio up to 32 dB. Devices lase at temperatures up to 105 °C with an extrapolated operational lifetime of 6.2 years at 35 °C.

Index Terms—Active-passive coupling, DBR laser, III-V on Si integration, monolithic integration, optical coupling, O-band, quantum dot laser, semiconductor laser, silicon photonics.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- The Evolution of Photonic Integrated Circuits and Silicon Photonics

- Monolithically Integrated Optical Through-Silicon Waveguides for 3D Chip-to-Chip Photonic Interconnects

- Foundry-Enabled Patterning of Diamond Quantum Microchiplets for Scalable Quantum Photonics

- Interfacing silicon photonics for high-density co-packaged optics

Latest Technical Papers

- A Review of Multiscale Thermal Modeling in Heterogeneous 3D ICs

- Spying Across Chiplets: Side-Channel Attacks in 2.5/3D Integrated Systems

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel