Link Quality Aware Pathfinding for Chiplet Interconnects

By Aaron Yen, Jooyeon Jeong, Puneet Gupta

University of California, Los Angeles, USA

Abstract

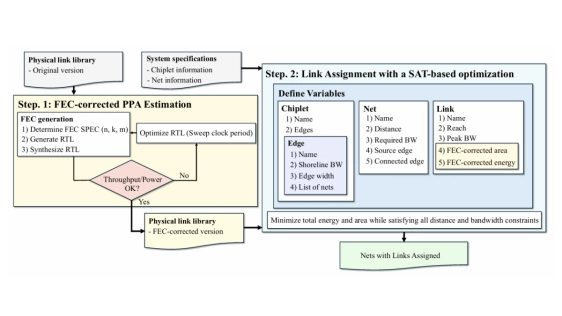

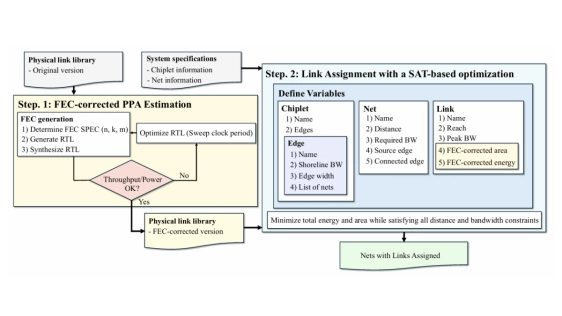

As chiplet-based integration advances, designers must select among short-reach die-to-die interconnect technologies with widely varying shoreline and areal bandwidth density, energy per bit, reach, and raw bit error rate (BER). Meeting stringent delivered BER targets in chiplet systems requires error-correcting codes (ECC), but incurs energy, area, and throughput overheads. We develop a flow centered around RTL synthesis power and area estimations to support pathfinding of inter-chiplet links under a stringent 10-27 delivered BER target. We synthesize a parameterized Reed-Solomon code with CRC-64 and Go-Back-N retry logic to estimate the correction overhead for different transceiver bit error rates. Results show that ECC can materially change link comparisons under common figures of merit and that CRC+ARQ can reduce the required RS strength (and decoder overhead) at moderate BERs while still meeting stringent delivered-BER targets. We present a CP-SAT-based link assignment formulation that uses these ECC-corrected metrics under reach, delivered-bandwidth, and shoreline constraints in system-level optimization.

As chiplet-based integration advances, designers must select among short-reach die-to-die interconnect technologies with widely varying shoreline and areal bandwidth density, energy per bit, reach, and raw bit error rate (BER). Meeting stringent delivered BER targets in chiplet systems requires error-correcting codes (ECC), but incurs energy, area, and throughput overheads. We develop a flow centered around RTL synthesis power and area estimations to support pathfinding of inter-chiplet links under a stringent 10-27 delivered BER target. We synthesize a parameterized Reed-Solomon code with CRC-64 and Go-Back-N retry logic to estimate the correction overhead for different transceiver bit error rates. Results show that ECC can materially change link comparisons under common figures of merit and that CRC+ARQ can reduce the required RS strength (and decoder overhead) at moderate BERs while still meeting stringent delivered-BER targets. We present a CP-SAT-based link assignment formulation that uses these ECC-corrected metrics under reach, delivered-bandwidth, and shoreline constraints in system-level optimization.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- High-Bandwidth Chiplet Interconnects for Advanced Packaging Technologies in AI/ML Applications: Challenges and Solutions

- Defect Analysis and Built-In-Self-Test for Chiplet Interconnects in Fan-out Wafer-Level Packaging

- Fault Modeling, Testing, and Repair for Chiplet Interconnects

- Optimizing Inter-chip Coupler Link Placement for Modular and Chiplet Quantum Systems

Latest Technical Papers

- CCD-Level and Load-Aware Thread Orchestration for In-Memory Vector ANNS on Multi-Core CPUs

- A Review of Multiscale Thermal Modeling in Heterogeneous 3D ICs

- Spying Across Chiplets: Side-Channel Attacks in 2.5/3D Integrated Systems

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving