Effects of Poor Workload Partitioning on System Performance for Chiplet-Based Systems

By Peter Mbua, Peter Forcha and Christophe Bobda

University of Florida, Gainesville, USA

Abstract

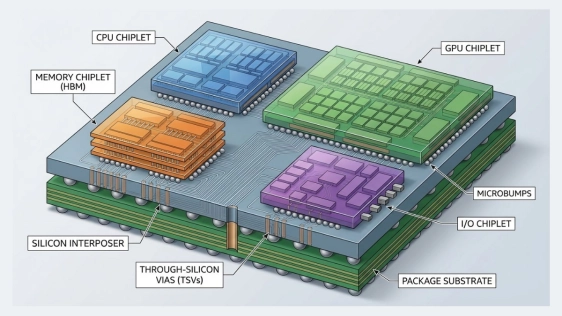

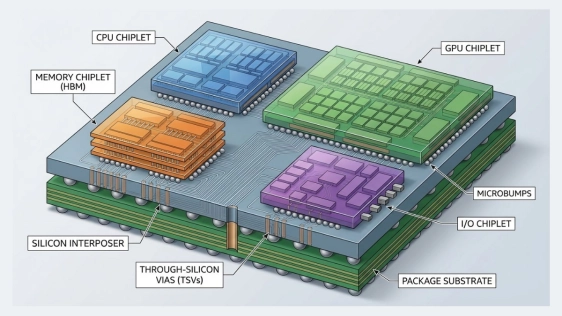

The emergence of chiplet-based architectures represents a paradigm shift in post-Moore’s Law computing systems, offering substantial cost and yield advantages through functional disaggregation. However, the heterogeneity of inter-chiplet communication introduces unique performance challenges that conventional partitioning strategies fail to address. In this work, the ways in which poor workload partitioning degrades communication performance in chiplet-based systems are comprehensively characterized. We demonstrate, through a detailed experimental analysis, that suboptimal workload partitioning can increase inter-chiplet communication latency by up to a factor of 10 and inflate network congestion beyond sustainable levels as systems scale. Our findings show that optimized partitioning strategies can achieve an 87.4% reduction in inter-chiplet traffic, improve system throughput by a factor of 8.75, and enhance energy efficiency by a factor of 10.3 compared to naive partitioning approaches. We further characterize how these effects scale with system size, revealing that the communication overhead can consume 85% of the execution time in poorly partitioned 16-chiplet systems, compared to only 35% in well-partitioned configurations. This work provides essential insights into the communication-aware design space of chiplet systems and validates the critical importance of sophisticated workload partitioning algorithms.

The emergence of chiplet-based architectures represents a paradigm shift in post-Moore’s Law computing systems, offering substantial cost and yield advantages through functional disaggregation. However, the heterogeneity of inter-chiplet communication introduces unique performance challenges that conventional partitioning strategies fail to address. In this work, the ways in which poor workload partitioning degrades communication performance in chiplet-based systems are comprehensively characterized. We demonstrate, through a detailed experimental analysis, that suboptimal workload partitioning can increase inter-chiplet communication latency by up to a factor of 10 and inflate network congestion beyond sustainable levels as systems scale. Our findings show that optimized partitioning strategies can achieve an 87.4% reduction in inter-chiplet traffic, improve system throughput by a factor of 8.75, and enhance energy efficiency by a factor of 10.3 compared to naive partitioning approaches. We further characterize how these effects scale with system size, revealing that the communication overhead can consume 85% of the execution time in poorly partitioned 16-chiplet systems, compared to only 35% in well-partitioned configurations. This work provides essential insights into the communication-aware design space of chiplet systems and validates the critical importance of sophisticated workload partitioning algorithms.

Keywords: chiplet-based systems; workload partitioning; task mapping; inter-chiplet communication; communication latency; network congestion

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- CATCH: a Cost Analysis Tool for Co-optimization of chiplet-based Heterogeneous systems

- CHIPSIM: A Co-Simulation Framework for Deep Learning on Chiplet-Based Systems

- CHICO-Agent: An LLM Agent for the Cross-layer Optimization of 2.5D and 3D Chiplet-based Systems

- Business Analysis of Chiplet-Based Systems and Technology

Latest Technical Papers

- A Review of Multiscale Thermal Modeling in Heterogeneous 3D ICs

- Spying Across Chiplets: Side-Channel Attacks in 2.5/3D Integrated Systems

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel