InterPUF: Distributed Authentication via Physically Unclonnable Functions and Multi-party Computation for Reconfigurable Interposers

By Ishraq Tashdid 1, Tasnuva Farheen 2, Sazadur Rahman 1

1 University of Central Florida, Orlando, FL, USA,

2 Louisiana State University, Baton Rouge, LA, USA

Abstract

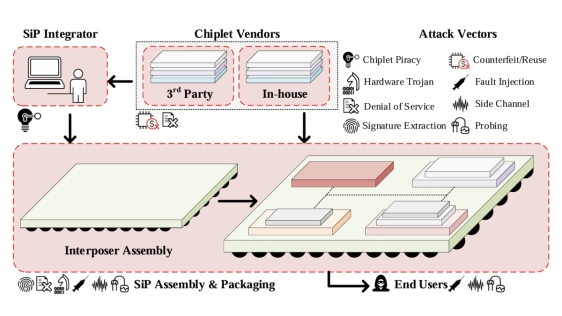

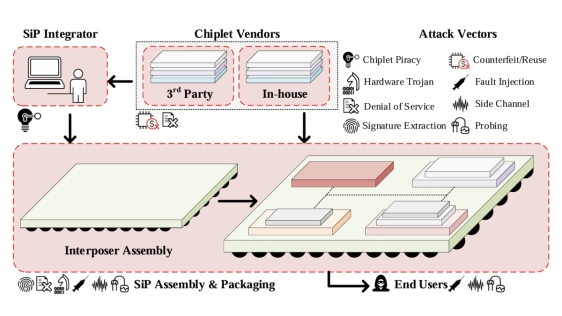

Modern system-in-Packages (SiP) platforms are rapidly adopting reconfigurable interposers to enable plug-and-play chiplet integration across heterogeneous multi-vendor ecosystem. However, this flexibility introduces severe trust challenges, as traditional security countermeasures fail to scale or adapt in these decentralized, post-fabrication programmable environments. This paper presents INTERPUF, a compact, scalable authentication framework that transforms the interposer into a distributed root of trust. At its core, INTERPUF embeds a route based differential delay Physical Unclonable Function (PUF) across the reconfigurable interconnect and secures its evaluation using multi-party computation (MPC). The proposed architecture introduces only 0.23% area and 0.072% power overhead across diverse chiplets while preserving authentication latency within tens of nanoseconds. Simulation results using PyPUF confirm strong uniqueness, reliability, and modeling resistance, even under process, voltage, and temperature variations. By fusing hardware-based PUF primitives with cryptographic hashing and collaborative verification, INTERPUF enforces a minimal-trust model without relying on any centralized anchor.

Modern system-in-Packages (SiP) platforms are rapidly adopting reconfigurable interposers to enable plug-and-play chiplet integration across heterogeneous multi-vendor ecosystem. However, this flexibility introduces severe trust challenges, as traditional security countermeasures fail to scale or adapt in these decentralized, post-fabrication programmable environments. This paper presents INTERPUF, a compact, scalable authentication framework that transforms the interposer into a distributed root of trust. At its core, INTERPUF embeds a route based differential delay Physical Unclonable Function (PUF) across the reconfigurable interconnect and secures its evaluation using multi-party computation (MPC). The proposed architecture introduces only 0.23% area and 0.072% power overhead across diverse chiplets while preserving authentication latency within tens of nanoseconds. Simulation results using PyPUF confirm strong uniqueness, reliability, and modeling resistance, even under process, voltage, and temperature variations. By fusing hardware-based PUF primitives with cryptographic hashing and collaborative verification, INTERPUF enforces a minimal-trust model without relying on any centralized anchor.

Index Terms — Secure Heterogeneous Integration, Physically Unclonable Function.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Garblet: Multi-party Computation for Protecting Chiplet-based Systems

- Thermo-mechanical co-design of 2.5D flip-chip packages with silicon and glass interposers via finite element analysis and machine learning

- DeepStack: Scalable and Accurate Design Space Exploration for Distributed 3D-Stacked AI Accelerators

- PICNIC: Silicon Photonic Interconnected Chiplets with Computational Network and In-memory Computing for LLM Inference Acceleration

Latest Technical Papers

- A Review of Multiscale Thermal Modeling in Heterogeneous 3D ICs

- Spying Across Chiplets: Side-Channel Attacks in 2.5/3D Integrated Systems

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel