Thermo-mechanical co-design of 2.5D flip-chip packages with silicon and glass interposers via finite element analysis and machine learning

By Mohammad Rafiee a, Farough Agin b , Kuldeep Kumar c , Ezhilan Murali c

a Department of Mechanical Engineering, University of Ottawa, Canada

b Department of Chemical and Biological Engineering, University of Ottawa, Canada

c School of Electrical Engineering and Computer Science, University of Ottawa, Canada

Abstract

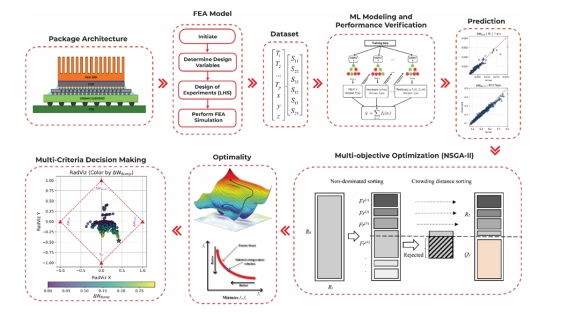

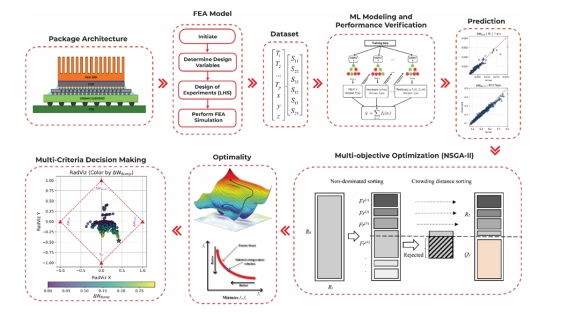

Advanced 2.5D flip-chip packages with silicon/glass interposers may pose tightly coupled thermo-mechanical trade-offs. This work presents a simulation-driven, machine-learning-assisted co-design framework that links high-fidelity finite-element analysis (FEA) with surrogate modeling, multi-objective optimization, and decision analysis. A 3D FEA model generates 500 Latin Hypercube design points for type of analysis (thermal and reliability), spanning geometry, materials, and thermal-path variables. Four minimized objectives are considered: junction-to-ambient thermal resistance (ΘJA) and cycle-averaged plastic strain-energy density at the corner flip- chip cu-pillar bump (ΔWbump), C4 bump (ΔWC4 ), and BGA (ΔWBGA ). Tree-based regressors (Random Forest, XGBoost) achieve high test-set fidelity and drive NSGA-II to enumerate the Pareto domain. A Net Flow multi-criteria decision method (MCDM) ranks Pareto candidates to identify a champion design with balanced thermo-mechanical performance. Re-simulation of the champion in FEA confirms surrogate accuracy for dominant responses (≈4–5 % deviation for ΔWbump and ΔWC4) and exact agreement for ΘJA , while revealing weak coupling between thermal and mechanical objectives—enabling partial decoupling of heat-path optimization from interconnect reliability.

Advanced 2.5D flip-chip packages with silicon/glass interposers may pose tightly coupled thermo-mechanical trade-offs. This work presents a simulation-driven, machine-learning-assisted co-design framework that links high-fidelity finite-element analysis (FEA) with surrogate modeling, multi-objective optimization, and decision analysis. A 3D FEA model generates 500 Latin Hypercube design points for type of analysis (thermal and reliability), spanning geometry, materials, and thermal-path variables. Four minimized objectives are considered: junction-to-ambient thermal resistance (ΘJA) and cycle-averaged plastic strain-energy density at the corner flip- chip cu-pillar bump (ΔWbump), C4 bump (ΔWC4 ), and BGA (ΔWBGA ). Tree-based regressors (Random Forest, XGBoost) achieve high test-set fidelity and drive NSGA-II to enumerate the Pareto domain. A Net Flow multi-criteria decision method (MCDM) ranks Pareto candidates to identify a champion design with balanced thermo-mechanical performance. Re-simulation of the champion in FEA confirms surrogate accuracy for dominant responses (≈4–5 % deviation for ΔWbump and ΔWC4) and exact agreement for ΘJA , while revealing weak coupling between thermal and mechanical objectives—enabling partial decoupling of heat-path optimization from interconnect reliability.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Business Analysis of Chiplet-Based Systems and Technology

- Codesign of quantum error-correcting codes and modular chiplets in the presence of defects

- The Evolution of Photonic Integrated Circuits and Silicon Photonics

- Analysis Of Multi-Chiplet Package Designs And Requirements For Production Test Simplification

Latest Technical Papers

- A Review of Multiscale Thermal Modeling in Heterogeneous 3D ICs

- Spying Across Chiplets: Side-Channel Attacks in 2.5/3D Integrated Systems

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel