Optimizing Inter-chip Coupler Link Placement for Modular and Chiplet Quantum Systems

By Zefan Du 1, Pedro Chumpitaz Flores 2, Wenqi Wei 1, Juntao Chen 1, Kaixun Hua 2, Ying Mao 1

1 Fordham University, New York, NY, USA

2 University of South Florida, Tampa, FL, USA

Abstract

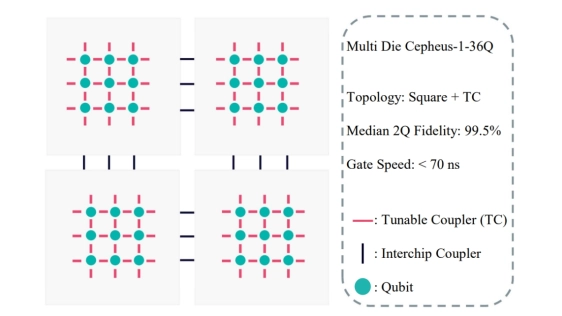

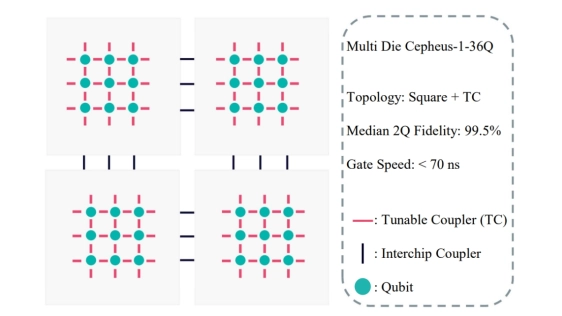

Quantum computing offers unparalleled computational capabilities but faces significant challenges, including limited qubit counts, diverse hardware topologies, and dynamic noise and error rates, which hinder scalability and reliability. Distributed quantum computing, particularly chip-to-chip connections, has emerged as a solution by interconnecting multiple processors to collaboratively execute large circuits. While hardware advancements, such as IBM's Quantum Flamingo, focus on improving inter-chip fidelity, limited research addresses efficient circuit cutting and qubit mapping in distributed systems. This project introduces InterPlace, a self-adaptive, hardware-aware framework for chip-to-chip distributed quantum systems. InterPlace analyzes qubit noise and error rates to construct a virtual system topology, guiding circuit partitioning and distributed qubit mapping to minimize SWAP overhead and enhance fidelity. Implemented with IBM Qiskit and compared with the state-of-the-art, InterPlace achieves up to a 53.0\% improvement in fidelity and reduces the combination of on-chip SWAPs and inter-chip operations by as much as 33.3\%, demonstrating scalability and effectiveness in extensive evaluations on real quantum hardware topologies.

Quantum computing offers unparalleled computational capabilities but faces significant challenges, including limited qubit counts, diverse hardware topologies, and dynamic noise and error rates, which hinder scalability and reliability. Distributed quantum computing, particularly chip-to-chip connections, has emerged as a solution by interconnecting multiple processors to collaboratively execute large circuits. While hardware advancements, such as IBM's Quantum Flamingo, focus on improving inter-chip fidelity, limited research addresses efficient circuit cutting and qubit mapping in distributed systems. This project introduces InterPlace, a self-adaptive, hardware-aware framework for chip-to-chip distributed quantum systems. InterPlace analyzes qubit noise and error rates to construct a virtual system topology, guiding circuit partitioning and distributed qubit mapping to minimize SWAP overhead and enhance fidelity. Implemented with IBM Qiskit and compared with the state-of-the-art, InterPlace achieves up to a 53.0\% improvement in fidelity and reduces the combination of on-chip SWAPs and inter-chip operations by as much as 33.3\%, demonstrating scalability and effectiveness in extensive evaluations on real quantum hardware topologies.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- FoldedHexaTorus: An Inter-Chiplet Interconnect Topology for Chiplet-based Systems using Organic and Glass Substrates

- Modular Compilation for Quantum Chiplet Architectures

- 3D-ICE 4.0: Accurate and efficient thermal modeling for 2.5D/3D heterogeneous chiplet systems

- TDPNavigator-Placer: Thermal- and Wirelength-Aware Chiplet Placement in 2.5D Systems Through Multi-Agent Reinforcement Learning

Latest Technical Papers

- A Review of Multiscale Thermal Modeling in Heterogeneous 3D ICs

- Spying Across Chiplets: Side-Channel Attacks in 2.5/3D Integrated Systems

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel