In-SoIC ESD Protection for Chiplet-Based 3D Microsystems: Future Research Directions

By Xunyu Li, Runyu Miao, Zijian Yue and Albert Wang

Department of Electrical and Computer Engineering, University of California, Riverside, USA

Abstract

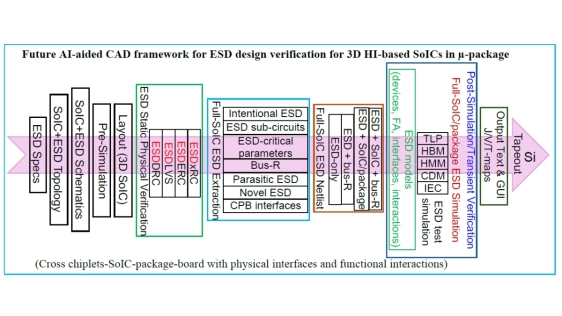

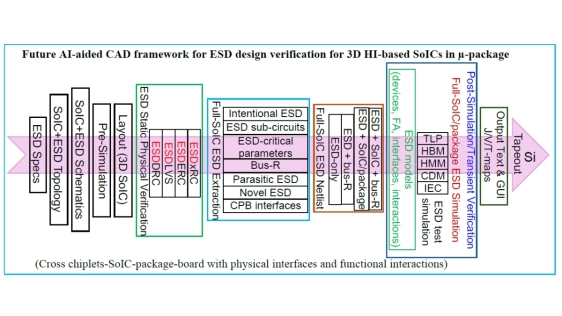

Heterogeneous integration opens a pathway to three-dimensional chiplet-based microsystem chips. Electrostatic discharge reliability is a major challenge to future smart chips featuring rich functionalities and ultra performance, utilizing advanced heterogeneous integration and packaging technologies. This paper discusses emerging challenges and future research directions in developing robust electrostatic discharge protection solutions for future systems-on-integrated-chiplets.

Heterogeneous integration opens a pathway to three-dimensional chiplet-based microsystem chips. Electrostatic discharge reliability is a major challenge to future smart chips featuring rich functionalities and ultra performance, utilizing advanced heterogeneous integration and packaging technologies. This paper discusses emerging challenges and future research directions in developing robust electrostatic discharge protection solutions for future systems-on-integrated-chiplets.

Keywords: electrostatic discharge; ESD protection; chiplet; SoIC; heterogeneous integration

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Towards efficient ESD protection strategies for advanced 3D systems-on-chip

- CHICO-Agent: An LLM Agent for the Cross-layer Optimization of 2.5D and 3D Chiplet-based Systems

- On hardware security and trust for chiplet-based 2.5D and 3D ICs: Challenges and Innovations

- System-Technology Co-Optimization for Dense Edge Architectures using 3D Integration and Non-Volatile Memory

Latest Technical Papers

- A Review of Multiscale Thermal Modeling in Heterogeneous 3D ICs

- Spying Across Chiplets: Side-Channel Attacks in 2.5/3D Integrated Systems

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel