Multi-Partner Project: COIN-3D -- Collaborative Innovation in 3D VLSI Reliability

By George Rafael Gourdoumanis †, Fotoini Oikonomou †, Maria Pantazi-Kypraiou †, Pavlos Stoikos †, Olympia Axelou †, Athanasios Tziouvaras †, Georgios Karakonstantis †, Tahani Aladwani +, Christos Anagnostopoulos +, Yixian Shen ‡, Anuj Pathania ‡, Alberto Garcia-Ortiz *, and George Floros †§

† Department of Electrical and Computer Engineering, University of Thessaly, Greece

+ School of Computing Science, University of Glasgow, UK

‡ University of Amsterdam, The Netherlands

* Institute of Electrodynamics and Microelectronics, University of Bremen, Germany

§ Department of Electronic and Electrical Engineering, Trinity College Dublin, Ireland

Abstract

As semiconductor manufacturing advances from the 3-nm process toward the sub-nanometer regime and transitions from FinFETs to gate-all-around field-effect transistors (GAAFETs), the resulting complexity and manufacturing chal lenges continue to increase. In this context, 3D chiplet-based approaches have emerged as key enablers to address these limitations while exploiting the expanded design space. Specifically, chiplets help address the lower yields typically associated with large monolithic designs. This paradigm enables the modular design of heterogeneous systems consisting of multiple chiplets (e.g., CPUs, GPUs, memory) fabricated using different technology nodes and processes. Consequently, it offers a capable and cost effective strategy for designing heterogeneous systems.

As semiconductor manufacturing advances from the 3-nm process toward the sub-nanometer regime and transitions from FinFETs to gate-all-around field-effect transistors (GAAFETs), the resulting complexity and manufacturing chal lenges continue to increase. In this context, 3D chiplet-based approaches have emerged as key enablers to address these limitations while exploiting the expanded design space. Specifically, chiplets help address the lower yields typically associated with large monolithic designs. This paradigm enables the modular design of heterogeneous systems consisting of multiple chiplets (e.g., CPUs, GPUs, memory) fabricated using different technology nodes and processes. Consequently, it offers a capable and cost effective strategy for designing heterogeneous systems.

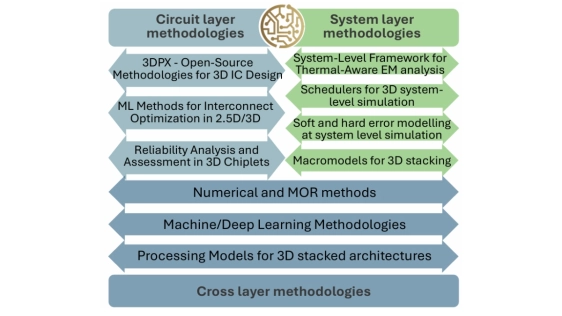

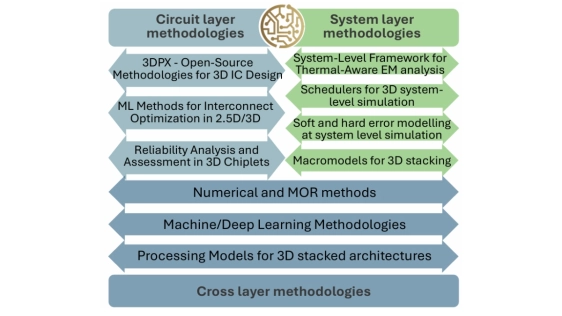

This paper introduces the Horizon Europe Twinning project COIN-3D (Collaborative Innovation in 3D VLSI Reliability), which aims to strengthen research excellence in 2.5D/3D VLSI systems reliability through collaboration between leading European institutions. More specifically, our primary scientific goal is the provision of novel open-source Electronic Design Automation (EDA) tools for reliability assessment of 3D systems, integrating advanced algorithms for physical- and system-level reliability analysis.

Index Terms — 3D VLSI, Chiplets, EDA Tools, Physical Design Methodologies, Architectural Exploration, Reliability

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Reliability challenges in 3D IC semiconductor design

- On hardware security and trust for chiplet-based 2.5D and 3D ICs: Challenges and Innovations

- Business Analysis of Chiplet-Based Systems and Technology

- Towards efficient ESD protection strategies for advanced 3D systems-on-chip

Latest Technical Papers

- CHICO-Agent: An LLM Agent for the Cross-layer Optimization of 2.5D and 3D Chiplet-based Systems

- A PPA-Driven 3D-IC Partitioning Selection Framework with Surrogate Models

- Fleet: Hierarchical Task-based Abstraction for Megakernels on Multi-Die GPUs

- ChipLight: Cross-Layer Optimization of Chiplet Design with Optical Interconnects for LLM Training

- ELMoE-3D: Leveraging Intrinsic Elasticity of MoE for Hybrid-Bonding-Enabled Self-Speculative Decoding in On-Premises Serving