Inter-chip Clock Network Synthesis on Passive Interposer of 2.5D Chiplet Considering Transmission Line Effect

By Tai Yan ‡, Yiyu Wang †,§, Zhan Li ¶, Ning Xu ‡, and Yuanqing Cheng †,§

† School of Integrated Circuit Science and Engineering, Beihang University, Beijing, China 100191

‡ School of Computer and Artificial Intelligence, Wuhan University of Technology, Wuhan, Hubei 430070

§ Shenzhen Institute of Beihang University, Shenzhen, China 518000

¶ School of Mathematical Science, Beihang University, Beijing, China 100191

Abstract

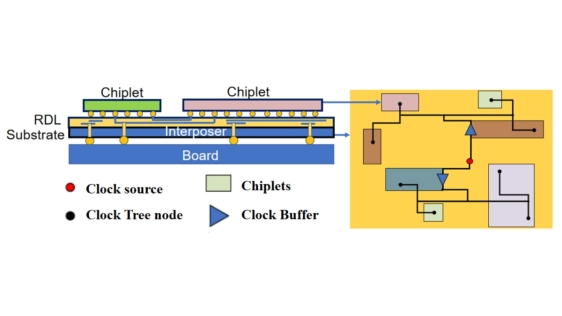

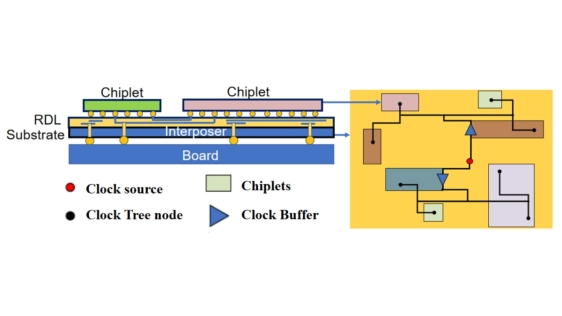

With the slowdown of technology node scaling, 2.5D Chiplet technology has emerged as a promising approach to sustain Moore’s Law. When routing clock signal on the passive interposer layer, transmission line effect must be considered, as signal rise/fall delay becomes comparable to propagation delay, significantly impacting signal integrity and system performance. Additionally, since active devices cannot be placed on the passive interposer, buffers can only be inserted in the chiplets mounted on the interposer. This paper investigates the problem of clock network synthesis for a 2.5D Chiplet with a passive interposer. Firstly, we propose to use a transmission line model to evaluate inter-chip clock skew and delay accurately. Then, we propose a clock network synthesis method considering transmission line effect and impedance matching. Finally, we propose a buffer insertion method with minimum clock wire detouring on passive interposer in order to optimize the inter-chiplet clock network. Experimental results show that our fast transmission line model can calculate clock skew more accurately compared to conventional Elmore model and only results in 2.4% error compared to HSPICE simulations. The clock network syntheses on several 2.5D Chiplet benchmarks show that our proposed algorithm is effective to construct zero-skew clock network for a 2.5D Chiplet in terms of clock skew and buffer area.

With the slowdown of technology node scaling, 2.5D Chiplet technology has emerged as a promising approach to sustain Moore’s Law. When routing clock signal on the passive interposer layer, transmission line effect must be considered, as signal rise/fall delay becomes comparable to propagation delay, significantly impacting signal integrity and system performance. Additionally, since active devices cannot be placed on the passive interposer, buffers can only be inserted in the chiplets mounted on the interposer. This paper investigates the problem of clock network synthesis for a 2.5D Chiplet with a passive interposer. Firstly, we propose to use a transmission line model to evaluate inter-chip clock skew and delay accurately. Then, we propose a clock network synthesis method considering transmission line effect and impedance matching. Finally, we propose a buffer insertion method with minimum clock wire detouring on passive interposer in order to optimize the inter-chiplet clock network. Experimental results show that our fast transmission line model can calculate clock skew more accurately compared to conventional Elmore model and only results in 2.4% error compared to HSPICE simulations. The clock network syntheses on several 2.5D Chiplet benchmarks show that our proposed algorithm is effective to construct zero-skew clock network for a 2.5D Chiplet in terms of clock skew and buffer area.

Index Terms: Transmission line model, clock network synthesis, passive interposer, buffer insertion, clock skew, 2.5D Chiplets

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- High-Efficient and Fast-Response Thermal Management by Heterogeneous Integration of Diamond on Interposer-Based 2.5D Chiplets

- DISTIL: A Distributed Spiking Neural Network Accelerator on 2.5D Chiplet Systems

- The Revolution of Chiplet Technology in Automotive Electronics and Its Impact on the Supply Chain

- Electrothermal co-optimization of 2.5D power distribution network with TTSV cooling

Latest Technical Papers

- Mozart: Modularized and Efficient MoE Training on 3.5D Wafer-Scale Chiplet Architectures

- Network Design for Wafer-Scale Systems with Wafer-on-Wafer Hybrid Bonding

- CarbonPATH: Carbon-aware pathfinding and architecture optimization for chiplet-based AI systems

- RPU -- A Reasoning Processing Unit

- Spatiotemporal thermal characterization for 3D stacked chiplet systems based on transient thermal simulation