Socionext Expands 3DIC Support with Advanced 3D Die Stacking and 5.5D in Packaging Portfolio

Production-Ready 3DIC Technology for Compact, Power-efficient Consumer Applications and High-performance AI and HPC Devices

[Yokohama, Japan, August 28, 2025] --- Socionext, the Solution SoC company, today announced the availability of 3DIC support in its portfolio of well-proven capabilities for the delivery of complete solutions for consumer, AI, and HPC data centerapplications that include chiplets, 2.5D, 3D, and 5.5D packaging. Socionext empowers customers with a proven development process and unmatched expertise delivering high- performance, high-quality solutions that accelerate innovation and success.

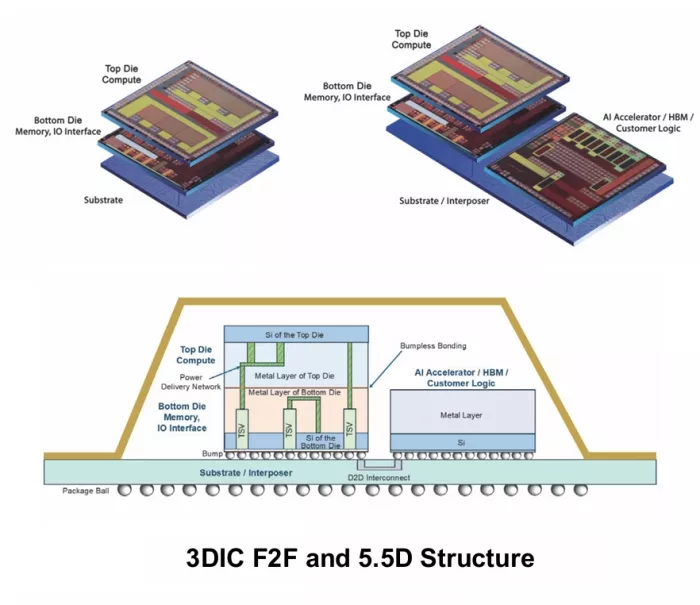

As a key milestone, Socionext has successfully taped out a complete packaged device leveraging TSMC’s SoIC-X 3D stacking. The design combines an N3 compute die and an N5 I/O die in a face-to-face (F2F) configuration. The F2F 3D stacking approach minimizes interconnect distance, significantly reduces signal latency and power consumption compared to traditional 2D and 2.5D designs.

Vertical Stacking, Limitless Potential with the 3DIC Design

Building on the company’s experience in 2.5D designs, Socionext applies proven design experience and methodologies to 3DICs, which stack components vertically to unlock key advantage3DIC F2F and 5.5D Structure

- Heterogeneous Integration

3D ICs enable the integration of different technology nodes (3nm, 5nm, 7nm) and functions (e.g., logic, memory, interface) into a single package, allowing for more optimally partitioned solution addressing performance, density, and cost.

- Higher Integration Density for a Broader Range of Applications

Vertical stacking enables greater functionality in a smaller footprint—an essential advantage as traditional scaling nears itslimits. This is especially valuable for space-constrained consumer devices.

- Improved Performance

Shorter, wider connections between dies reduce latency and boost bandwidth.

- Lower Power Consumption

Compact interconnects result in reduced drive requirements due to lower impedance.

A Vision for the Future

The introduction of 3DIC along with 5.5D support reflects Socionext’s strong focus on advancing heterogeneous integration, bringing together multiple functions within a unified system of semiconductors and packaging elements. As demand grows for scalable, high-density, and energy-efficient platforms, especially in consumer, AI, and data center applications, 3DICs will play apivotal role in shaping the future of semiconductor innovation.

“Socionext’s extensive experience in SoC design and our collaboration with TSMC position us at the forefront of next-generationSoC development,” said Rajinder Cheema, CTO and Executive Vice President at Socionext. “This milestone reflects our dedication to delivering cutting-edge solutions that meet the evolving needs of our customers.”

About Socionext Inc.

Socionext Inc., a leading global System-on-Chip (SoC) supplier, is a pioneer of the ‘Solution SoC’ business model. Thisinnovative approach encompasses Socionext’s ‘Entire Design’ capabilities and offering of ‘Complete Service’. As a trusted siliconpartner, Socionext fuels global innovation, providing superior features, performance, and quality that set its customers’ productsand services apart in diverse domains ranging from automotive and data centers to networking, smart devices, and industrial equipment.

Socionext Inc., based in Yokohama, operates offices across Japan, Asia, the United States, and Europe for development and sales. For more information, visit https://www.socionext.com/en/.

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- Catching Up on The Latest in Advanced Packaging at SEMICON Europa 2024

- Onshoring Advanced Packaging Update

- Siemens and Intel Foundry advance their collaboration to enable cutting-edge integrated circuits and advanced packaging solutions for 2D and 3D IC

- Advanced IC Packaging: The Roadmap to 3D IC Semiconductor Scaling

Latest News

- GUC Announces Tape-out of UCIe 64G IP on TSMC N3P Technology

- GLS and APES Announce Advanced Semiconductor Packaging Partnership

- Ayar Labs Names Sankara Venkateswaran as Vice President of Engineering

- Baya Systems and Aion Silicon Partner to Accelerate Next-Generation SoC and Chiplet Designs

- ADTechnology and Fraunhofer IIS Join Forces for Advanced ASIC and Chiplet Development