Chiplet technology for large-scale trapped-ion quantum processors

By Bassem Badawi 1, Philip C. Holz 2, Michael Raffetseder 1, Nicolas Jungwirth 1, Juris Ulmanis 2, Hans-Joachim Quenzer 3, Dirk Kahler 3, Thomas Monz 1,2, and Philipp Schindler 1

1 University of Innsbruck, Institute of Experimental Physics, Austria

2 Alpine Quantum Technologies GmbH, Austria

3 Fraunhofer Institute for Silicon Technology ISIT, Germany

Abstract

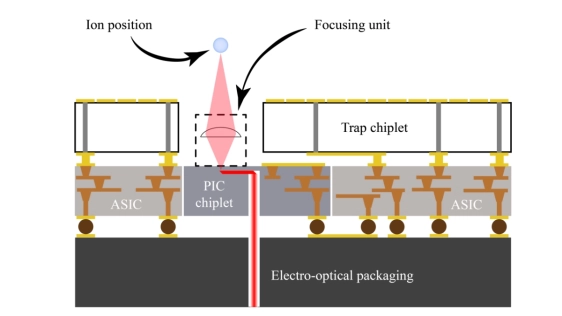

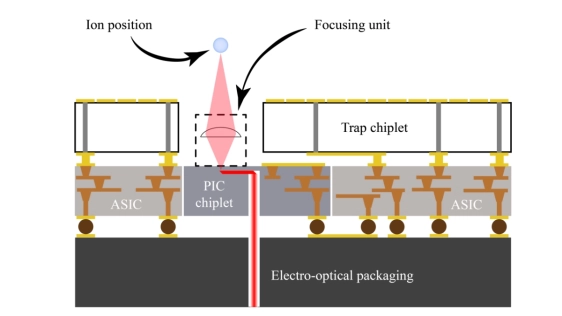

Trapped ions are among the most promising platforms for realizing a large-scale quantum information processor. Current progress focuses on integrating optical and electronic components into microfabricated ion traps to allow scaling to large numbers of ion qubits. Most available fabrication strategies for such integrated processors employ monolithic integration of all processor components and rely heavily on CMOS-compatible semiconductor fabrication technologies that are not optimized for the requirements of a trapped-ion quantum processor. In this work, we present a modular approach in which the processor modules, called chiplets, have specific functions and are fabricated separately. The individual chiplets are then combined using heterogeneous integration techniques. This strategy opens up the possibility of choosing the optimal materials and fabrication technology for each of the chiplets, with a minimum amount of fabrication limitations compared to the monolithic approach. Chiplet technology furthermore enables novel processor functionalities to be added in a cost-effective, modular fashion by adding or modifying only a subset of the chiplets. We describe the design concept of a chiplet-based trapped-ion quantum processor and demonstrate the technology with an example of an integrated individual-ion addressing system for a ten-ion crystal. The addressing system emphasizes the modularity of the chiplet approach, combining a surface ion trap manufactured on a glass substrate with a silicon substrate carrying integrated waveguides and a stack of 3D-printed micro-optics, achieving diffraction-limited focal spots at the ion positions.

Trapped ions are among the most promising platforms for realizing a large-scale quantum information processor. Current progress focuses on integrating optical and electronic components into microfabricated ion traps to allow scaling to large numbers of ion qubits. Most available fabrication strategies for such integrated processors employ monolithic integration of all processor components and rely heavily on CMOS-compatible semiconductor fabrication technologies that are not optimized for the requirements of a trapped-ion quantum processor. In this work, we present a modular approach in which the processor modules, called chiplets, have specific functions and are fabricated separately. The individual chiplets are then combined using heterogeneous integration techniques. This strategy opens up the possibility of choosing the optimal materials and fabrication technology for each of the chiplets, with a minimum amount of fabrication limitations compared to the monolithic approach. Chiplet technology furthermore enables novel processor functionalities to be added in a cost-effective, modular fashion by adding or modifying only a subset of the chiplets. We describe the design concept of a chiplet-based trapped-ion quantum processor and demonstrate the technology with an example of an integrated individual-ion addressing system for a ten-ion crystal. The addressing system emphasizes the modularity of the chiplet approach, combining a surface ion trap manufactured on a glass substrate with a silicon substrate carrying integrated waveguides and a stack of 3D-printed micro-optics, achieving diffraction-limited focal spots at the ion positions.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Optimized Low Parasitic Capacitance ESD Clamps for High-Bandwidth 2.5D/3D Chiplet Interfaces in Advanced FinFET Technology

- Modular Compilation for Quantum Chiplet Architectures

- ATPlace2.5D: Analytical Thermal-Aware Chiplet Placement Framework for Large-Scale 2.5D-IC

- Optimizing Inter-chip Coupler Link Placement for Modular and Chiplet Quantum Systems

Latest Technical Papers

- A Review of Multiscale Thermal Modeling in Heterogeneous 3D ICs

- Spying Across Chiplets: Side-Channel Attacks in 2.5/3D Integrated Systems

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel