AuthenTree: A Scalable MPC-Based Distributed Trust Architecture for Chiplet-based Heterogeneous Systems

By Ishraq Tashdid 1, Tasnuva Farheen 2, Sazadur Rahman 1

1 University of Central Florida, Orlando, FL, USA,

2 Louisiana State University, Baton Rouge, LA, USA

Abstract

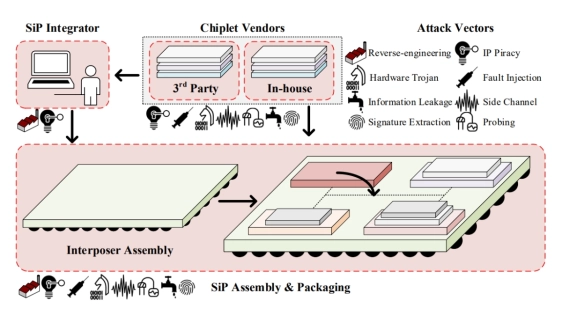

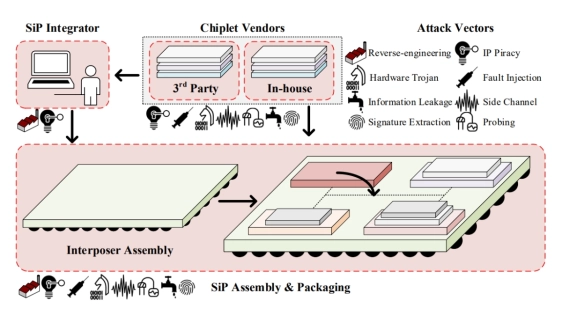

The rapid adoption of chiplet-based heterogeneous integration is reshaping semiconductor design by enabling modular, scalable, and faster time-to-market solutions for AI and high-performance computing. However, multi-vendor assembly in post-fabrication environments fragments the supply chain and exposes SiP systems to serious security threats, including cloning, overproduction, and chiplet substitution. Existing authentication solutions depend on trusted integrators or centralized security anchors, which can expose sensitive data or create single points of failure. We introduce AuthenTree, a distributed authentication framework that leverages multi-party computation (MPC) in a scalable tree-based architecture, removing the need for dedicated security hardware or centralized trust. AuthenTree enables secure chiplet validation without revealing raw signatures, distributing trust across multiple integrator chiplets. Our evaluation in five SiP benchmarks demonstrates that AuthenTree imposes minimal overhead, with an area as low as 0.48% (7,000μm2), an overhead power under 0.5%, and an authentication latency below 1μs, bypassing previous work in some cases 700×. These results establish AuthenTree as an efficient, robust, and scalable solution for next-generation chiplet-based security in zero-trust SiP environments.

The rapid adoption of chiplet-based heterogeneous integration is reshaping semiconductor design by enabling modular, scalable, and faster time-to-market solutions for AI and high-performance computing. However, multi-vendor assembly in post-fabrication environments fragments the supply chain and exposes SiP systems to serious security threats, including cloning, overproduction, and chiplet substitution. Existing authentication solutions depend on trusted integrators or centralized security anchors, which can expose sensitive data or create single points of failure. We introduce AuthenTree, a distributed authentication framework that leverages multi-party computation (MPC) in a scalable tree-based architecture, removing the need for dedicated security hardware or centralized trust. AuthenTree enables secure chiplet validation without revealing raw signatures, distributing trust across multiple integrator chiplets. Our evaluation in five SiP benchmarks demonstrates that AuthenTree imposes minimal overhead, with an area as low as 0.48% (7,000μm2), an overhead power under 0.5%, and an authentication latency below 1μs, bypassing previous work in some cases 700×. These results establish AuthenTree as an efficient, robust, and scalable solution for next-generation chiplet-based security in zero-trust SiP environments.

Index Terms:

Chiplet Integration, Hardware Security, Multi-party Computation (MPC), Authentication, Trust Architecture

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- CATCH: a Cost Analysis Tool for Co-optimization of chiplet-based Heterogeneous systems

- CarbonPATH: Carbon-aware pathfinding and architecture optimization for chiplet-based AI systems

- DCRA: A Distributed Chiplet-based Reconfigurable Architecture for Irregular Applications

- ChipAI: A scalable chiplet-based accelerator for efficient DNN inference using silicon photonics

Latest Technical Papers

- A Review of Multiscale Thermal Modeling in Heterogeneous 3D ICs

- Spying Across Chiplets: Side-Channel Attacks in 2.5/3D Integrated Systems

- Affinity Tailor: Dynamic Locality-Aware Scheduling at Scale

- AMMA: A Multi-Chiplet Memory-Centric Architecture for Low-Latency 1M Context Attention Serving

- Exploring the Efficiency of 3D-Stacked AI Chip Architecture for LLM Inference with Voxel