A Chiplet-Optimized Unified Fabric Interconnect Solution

Chiplets, the vanguard of semiconductor chip evolution, are revolutionizing the industry by addressing performance and cost. With new standards and ever-advancing packaging technology, chiplets offer innovative ways to construct superior, more optimized chip solutions. Their potential in AI, a field that has seen a surge in compute demand, particularly in generative AI, is truly inspiring. Chiplets are pivotal in scaling AI processing, enabling the ideal mix of CPU, GPU, NPU, custom accelerators, and other components in the right process technologies for efficient and power-optimized designs based on the application and workload.

Multi-die Complexities

As the industry transitions from SoC to chiplet-based architectures, a new Network-on-chip (NoC) technology has the potential to make things much easier. Almost all modern SoC designs use Networks on Chip (NoCs) to move data between heterogeneous computing elements while minimizing the resources required to connect them. NoCs extend seamlessly across an SoC, but multi-die implementations introduce another layer of complexity to fabric and cache architecture. However, these complexities can be overcome with the proper understanding and implementation, paving the way for a more efficient and optimized chip design future.

Chiplet-Optimized NoC

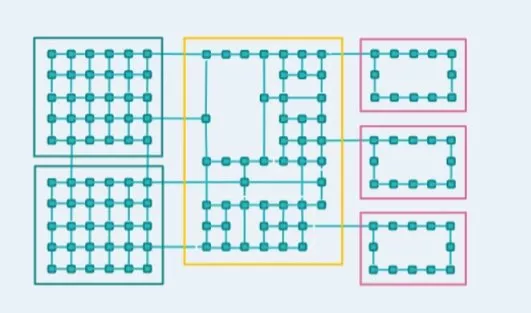

Baya Systems and Blue Cheetah, two industry frontrunners, have combined their expertise to develop a revolutionary chiplet-optimized NoC and physical link (PHY) interconnect IP solution. While connecting NoCs on individual chiplets through the D2D PHY is possible today, Baya’s unique approach integrates the various NoCs into a unified fabric that functions like an intelligent global NoC. The solution efficiently and seamlessly handles latency, bandwidth, and throughput requirements and provides flexibility in traffic routing systemwide in multi-die designs. It optimizes and simplifies the communication infrastructure, freeing systems designers to focus on the value-added part of the system and decide to incorporate external interfaces and third-party IP chiplets much later in the design cycle. It also provides the flexibility to scale a system both heterogeneously and homogeneously, allowing system designers to explore new horizons in chiplet design.

Tenstorrent, the firm led by legendary chip architect Jim Keller, the mastermind behind Tesla’s original self-driving chip, recently announced it is using Baya’s new Weave IP™ NoC and Blue Cheetah’s BlueLynx™ PHY IP to scale its AI and RISC-V chiplet solutions. Keller commented that the tools start with top-level architecture that allows them to plan at a detailed level, including performance modeling, transport, quality of service, and cache coherency. He added that the solution provides a fabric IP that delivers the performance and scale Tenstorrent’s designers need to build next-generation chiplet-based solutions.

A Bridge between Chiplets

Designers of chiplet-based systems can harness the capabilities of Baya Systems’ WeaverPro, Cache Studio, and Fabric Studio software. These tools are instrumental in designing a NoC that spans multiple chiplets. At each bridge between chiplets, Blue Cheetah’s D2D PHY interfaces provide a low-energy interface that can be customized to the bandwidth needs of that specific part of the network. This comprehensive software suite and interface solution offer a powerful combination for efficient and optimized chiplet-based system design.

Blue Cheetah, a trailblazer in the industry, has solidified its position with high-speed, low-latency, power-efficient D2D BlueLynx™ interface products. These state-of-the-art IP solutions are available now in 16nm,12nm, 7nm, 6nm, 5nm, 4nm, 3nm, and below across multiple semiconductor foundries. BlueLynx offers versatile packaging options, including standard and advanced, supporting multiple bump pitches, metal stacks, and poly orientations. BlueLynx™ seamlessly integrates with on-die buses using popular standards like AMBA® CHI, AXI, ACE, and more while also accommodating the Universal Chiplet Interconnect Express (UCIe) or Open Compute Project (OCP) Bunch of Wires (BoW) standards.

Figure 1 Baya’s unique approach integrates the various NoCs into a unified fabric that functions like an intelligent global NoC in multi-die systems.

To learn more, visit https://bayasystems.com/ and https://www.bcanalog.com/

Related Chiplet

- High Performance Droplet

- Interconnect Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Bridglets

- Automotive AI Accelerator

Related Blogs

- A System Architect’s Guide to Multi-Die Interconnect

- A Smarter Path To Chiplets Through An Enhanced Multi-Die Solution

- Interconnect Is All You Need: Final Nodes, Big Chips, and Photonics

- Integrated Modular Firmware Solutions: A Vital Component of Custom Silicon Chiplet Architecture Designs

Latest Blogs

- Accelerating Chiplet Integration in Heterogeneous IC Package Designs

- Visualizing Cross-Die Paths in Multi-Die Designs

- 5 Chiplets Design Challenges Hampering Wider Take-off

- Scalable Testing of Xanadu’s Canadian made Quantum Photonic Chips with MPI Corporation’s Advanced Electro-Optic Probe Systems

- Addressing challenges and embracing advances with photonic package design