Geometry Challenges in Multidie Thermal Management

By Emily Newton, EETimes | December 4, 2025

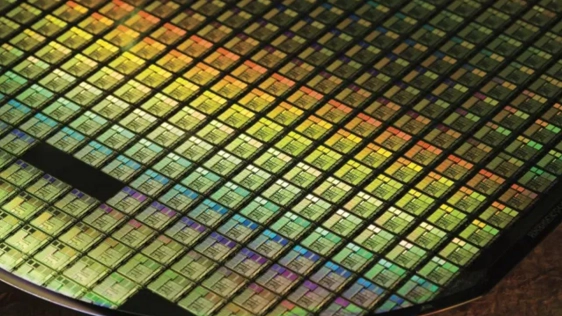

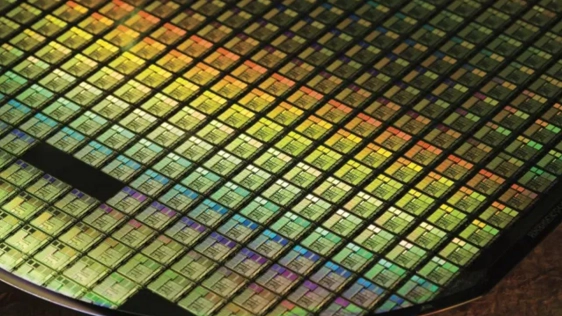

Three-dimensional, stacked semiconductor architectures create unique geometric challenges for multidie assembly, especially in managing heat. Designers must anticipate how geometry affects thermal distribution and proactively address these obstacles for successful designs.

Three-dimensional, stacked semiconductor architectures create unique geometric challenges for multidie assembly, especially in managing heat. Designers must anticipate how geometry affects thermal distribution and proactively address these obstacles for successful designs.

Heat buildup causes localized hot spots

Some designers wrongly assume a die’s power use is uniform. In reality, it varies greatly, creating areas of intense, localized heat.

Relatedly, the design constraints of a three-dimensional stack largely prevent heat from traveling sideways. Instead, it usually rises, potentially transferring the heat to the dies above it. The geometrical designs of multidie assemblies also result in these products having larger horizontal dimensions than vertical ones, which can further complicate the heat buildup.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- Benefits And Challenges In Multi-Die Assemblies

- Multi-Die Design Complicates Data Management

- Challenges In Managing Chiplet Resources

- Lam Research Introduces VECTOR® TEOS 3D to Address Critical Advanced Packaging Challenges in Chipmaking

Latest News

- NanoIC opens access to first-ever fine-pitch RDL and D2W hybrid bonding interconnect PDKs

- GUC Announces Tape-out of UCIe 64G IP on TSMC N3P Technology

- GLS and APES Announce Advanced Semiconductor Packaging Partnership

- Ayar Labs Names Sankara Venkateswaran as Vice President of Engineering

- Baya Systems and Aion Silicon Partner to Accelerate Next-Generation SoC and Chiplet Designs