Fault Modeling, Testing, and Repair for Chiplet Interconnects

By Xiaoting Liu a, Xiaojun Zhou a, Chengcheng Fu b, Dazhi Yang a, Suning Ji a, Nan Zhang b, Dapeng Yan a, Zixuan Wang a, Yufeng Guo a, Zhikuang Cai a

a Nanjing University of Posts and Telecommunications, 9 Wenyuan Road, Nanjing 210023, China

b China Aerospace Science & Industry Corp Defense Technology R&T Center, Beijing 100854, China

Abstract

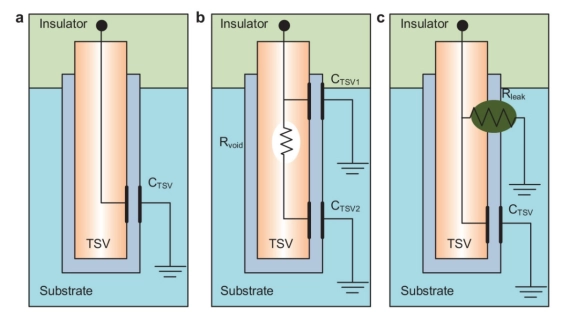

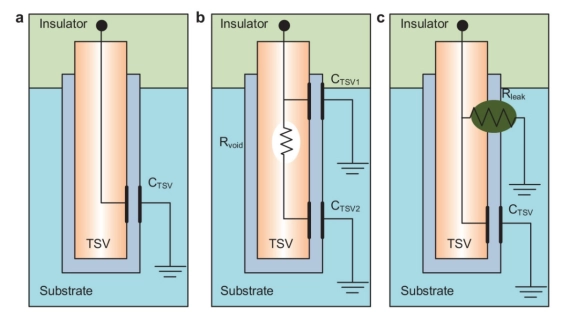

With the continuous advancement of semiconductor technology, chiplet technology has gained importance due to its significant advantages in enhancing performance, reducing power consumption, and saving space. However, vertical interconnect structures in 3D ICs, such as TSV (Through-Silicon Via) and ILV (Inter-Layer Via), present unprecedented challenges in modeling, testing and repair. This paper focuses on four modules: modeling for faults, TSV testing, ILV testing, and repair strategies. First, different methods of establishing TSV fault models and discusses the influence of different defects on performance are introduced. Then the challenges in detecting various faults of TSVs, such as short, delay faults, and crosstalk, and presents corresponding testing methods are analyzed. Meanwhile, some electric parameter test methods are also discussed. In the ILV testing technology, the difficulties caused by the small size and high density of ILVs, which make traditional testing methods less effective are discussed. Various testing and optimization methods are explored, aimed at improving fault coverage while minimizing testing time and hardware overhead. Moreover, repair strategies based on redundant TSVs are analyzed in this paper. Redundant repair architectures, including ring-based, honeycomb, and so on, are introduced. Additionally, the paper explores dynamic real-time fault repair methods, such as Time-Division Multiple Access (TDMA) and online repair technologies, which aim to enhance the reliability and lifespan of 3D ICs. In conclusion, a comprehensive solution for the testing of 3D chiplet is presented.

With the continuous advancement of semiconductor technology, chiplet technology has gained importance due to its significant advantages in enhancing performance, reducing power consumption, and saving space. However, vertical interconnect structures in 3D ICs, such as TSV (Through-Silicon Via) and ILV (Inter-Layer Via), present unprecedented challenges in modeling, testing and repair. This paper focuses on four modules: modeling for faults, TSV testing, ILV testing, and repair strategies. First, different methods of establishing TSV fault models and discusses the influence of different defects on performance are introduced. Then the challenges in detecting various faults of TSVs, such as short, delay faults, and crosstalk, and presents corresponding testing methods are analyzed. Meanwhile, some electric parameter test methods are also discussed. In the ILV testing technology, the difficulties caused by the small size and high density of ILVs, which make traditional testing methods less effective are discussed. Various testing and optimization methods are explored, aimed at improving fault coverage while minimizing testing time and hardware overhead. Moreover, repair strategies based on redundant TSVs are analyzed in this paper. Redundant repair architectures, including ring-based, honeycomb, and so on, are introduced. Additionally, the paper explores dynamic real-time fault repair methods, such as Time-Division Multiple Access (TDMA) and online repair technologies, which aim to enhance the reliability and lifespan of 3D ICs. In conclusion, a comprehensive solution for the testing of 3D chiplet is presented.

Keywords: Chiplet, Test, Repair, Interconnect, M3D

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- High-Bandwidth Chiplet Interconnects for Advanced Packaging Technologies in AI/ML Applications: Challenges and Solutions

- Defect Analysis and Built-In-Self-Test for Chiplet Interconnects in Fan-out Wafer-Level Packaging

- Fast and Accurate Jitter Modeling for Statistical BER Analysis for Chiplet Interconnect and Beyond

- 3D-ICE 4.0: Accurate and efficient thermal modeling for 2.5D/3D heterogeneous chiplet systems

Latest Technical Papers

- Spatiotemporal thermal characterization for 3D stacked chiplet systems based on transient thermal simulation

- Interconnect-Aware Logic Resynthesis for Multi-Die FPGAs

- Scope: A Scalable Merged Pipeline Framework for Multi-Chip-Module NN Accelerators

- Scaling Routers with In-Package Optics and High-Bandwidth Memories

- TDPNavigator-Placer: Thermal- and Wirelength-Aware Chiplet Placement in 2.5D Systems Through Multi-Agent Reinforcement Learning