The Evolution of Interconnects in Microelectronics Packaging

By Dr. Dongkai Shangguan

3DIncites (November 14, 2024)

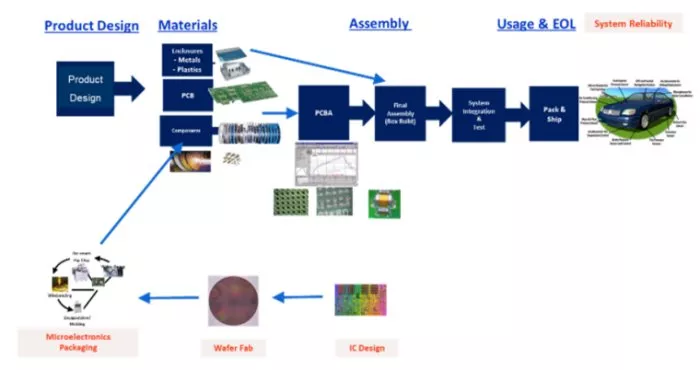

Semiconductor packaging is a complex and evolving field, involving multiple disciplines. As a microelectronics packaging engineer, I focus on the “interconnect thread” from the chip to the system (Figure 1).

To me, packaging is about interconnectivity (essentially). The primary function of packaging is to provide the interconnection from the IC to the system, for signal distribution and power distribution. What makes it more complex (and thus interesting) is the enabling functions, including mechanical reliability (especially under complex loading conditions in diverse use environments – thus various failure modes and mechanisms); thermal dissipation (especially important for high power and also due to the multiple interfaces in the system); as well as manufacturability that has to be considered (such as low temperature soldering, fine pitch processes, cost and quality, and very importantly, sustainability). These electro-mechano-thermal functions of the interconnect are what makes “packaging” such a critical area for semiconductor technology today. In the age of heterogeneous integration, a variety of interconnects in the same package have to be considered.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- How do UCIe and BoW interconnects support generative AI on chiplets?

- How can in-package optical interconnects enhance chiplet generative AI performance?

- How does UCIe on chiplets enable optical interconnects in data centers?

- NTT looks to 15Tbit/s chiplet optical interconnects

Latest News

- Tower Semiconductor Signs Customer Contracts for $1.3 Billion Silicon Photonics Revenue for 2027

- IC-Link by imec joins TSMC 3DFabric® Alliance to accelerate advanced packaging and 3D IC innovation

- EXTOLL announces Availability of Industry's first 16G UCIe PHY IP in GlobalFoundries 22FDX/22FDX+ Ready for Customer Integration

- NHanced Semiconductors & the University of Florida to Present on Hybrid Bonding Reliability at the 2026 Electronic Components & Technology Conference in Orlando

- Wooptix Targets AI Packaging Bottleneck with Astronomy Tech