Building the Foundation for an Open Chiplet Future: Foundation Chiplet System Architecture (FCSA)

“The future of Silicon is Modular, Scalable, and Standardized Chiplets”

The rapid acceleration of the AI economy is reshaping global compute infrastructure. From hyperscale data centers training trillion-parameter models to edge devices running AI inference locally, the demand for compute performance, memory bandwidth, and energy efficiency has never been higher. Traditional monolithic SoC scaling can no longer keep pace with AI’s diverse and ever-expanding workloads. As a result, the industry is embracing chiplets - modular silicon components that enable flexible system composition, faster innovation cycles, and more efficient use of advanced process technologies.

To truly unlock the potential of modular silicon, the industry needs well-defined common chiplet standards that allow chiplets from different vendors and architectures to work together seamlessly. This openness is essential to scaling the AI economy efficiently, fostering collaboration, and accelerating innovation across the entire compute landscape.

Introducing the Foundation Chiplet System Architecture (FCSA)

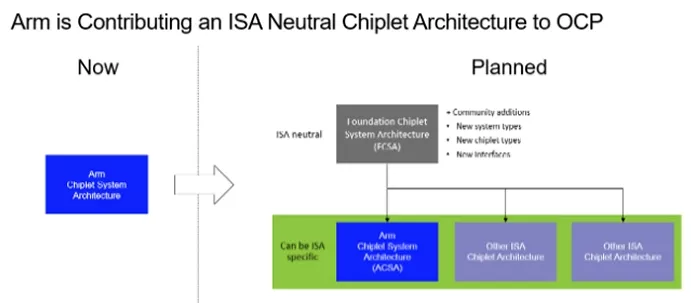

In February 2024, Arm introduced the Chiplet System Architecture (CSA), a specification defining how Arm-based systems can be functionally partitioned into reusable chiplets such as compute, IO expansion, and accelerator. CSA has been adopted across Arm’s ecosystem to standardize chiplet types, interfaces, and integration methodologies, enabling consistent multi-die system design.

Announced at OCP Global Summit 2025, Foundation Chiplet System Architecture (FCSA) leverages our ongoing work with the Arm CSA but addresses an industry demand for a framework that aligns with vendor- and CPU architecture-neutral requirements. It delivers a common set of standards for chiplet systems and interface definitions, accelerating chiplet design and integration while enabling reuse and interoperability at scale – regardless of CPU architecture. Its interfaces, protocols, and functions are defined at the hardware and fabric level, not tied to the processor instruction set running inside another chiplet. The FCSA will be developed and maintained under the OCP Open Chiplet Economy initiative, aligning with OCP’s mission to promote open standards and interoperability across data center and edge infrastructure. Arm’s own Mark Knight, a key driver of the FCSA contribution to the OCP Community, has recently joined the OCP Open Chiplet Economy group as a co-lead."

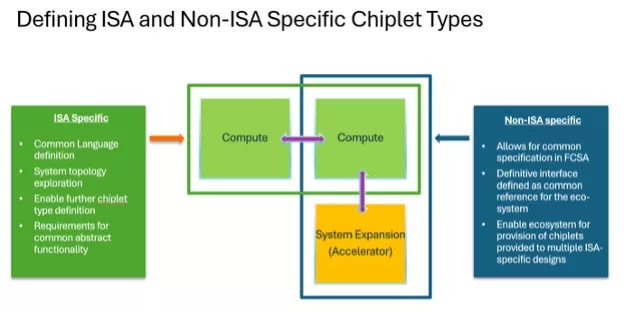

Over time, there will be a need for a range of ISA-specific and non-ISA-specific chiplet integrations. Therefore, the Arm CSA and FCSA will continue to be developed in lock step.

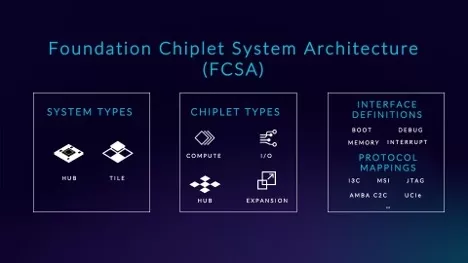

The FCSA provides:

- An Open, ISA-neutral, Architecture-Agnostic Foundation: The FCSA defines common chiplet types, interfaces, and behaviors that apply regardless of underlying CPU architecture.

- Standardized Interoperability Layers: It describes how functional, physical, and protocol layers interconnect chiplets using industry standards such as UCIe, AMBA CHI C2C, PCIe, and CXL, ensuring multi-vendor interoperability.

- A common Language for System Integration: FCSA introduces a taxonomy of chiplet types - Compute, Accelerator, I/O, Memory, and System Expansion, enabling consistent classification and compatibility across the ecosystem. This eliminates fragmentation, establishes a common language, simplifies design, and enables an open ecosystem for chiplet integration.

- A community-driven extensibility: The FCSA will evolve through OCP collaboration, allowing partners to propose new chiplet types, interfaces, and use cases as technologies mature.

- Open Licensing and Collaboration: Hosted within the OCP framework, the FCSA is available under permissive licensing terms, open governance, encouraging adoption, reuse, and derivative work across the semiconductor industry.

The FCSA defines a layered chiplet integration model, aligning system functionality, interface protocols, and physical integration:

- System Design Layer – Defines system partitioning into chiplet types (Compute, Accelerator, I/O, etc.).

- Functional Interface Layer – Specifies required interfaces: memory, coherency, interrupts, security, control, debug, etc.

- Transport Layer – Maps interfaces onto standard interconnects (e.g., UCIe, AMBA CHI-C2C, CXL, PCIe).

- Physical Layer – Covers packaging, interposer, and 3D interconnects (handled by other OCP subprojects).

FCSA defines common chiplet classes that can be extended by specific architectures or vendors:

- Compute Chiplets – Contain CPU cores, memory controllers, and caches.

- Accelerator Chiplets – AI, graphics, or DSP engines (can be coherent or I/O coherent).

- Expansion Chiplets – Provide additional compute or I/O features.

- I/O Coherent Chiplets – Manage coherent I/O interfaces (e.g., PCIe, CXL).

- System Management Chiplets – Include security, power, and control logic.

Each chiplet type has defined interface expectations and trust boundary rules, making them composable across systems.

Why collaborate around the Foundation Chiplet System Architecture at OCP?

Collaborating around the Foundation Chiplet System Architecture (FCSA) at the Open Compute Project (OCP) ensures that the future of multi-die systems evolves as a shared, open, and interoperable ecosystem rather than a fragmented collection of proprietary solutions. The OCP community provides a neutral, collaborative environment where chipmakers, IP providers, foundries, and system integrators can define and align on a common foundation for chiplet interoperability.

The benefits extend across the entire semiconductor value chain. Chiplet producers gain access to a larger market by building to shared, ISA-neutral definitions that make their products reusable across platforms. Chiplet consumers, such as system integrators and OEMs, benefit from reduced design complexity, lower integration costs, and the ability to source interoperable chiplets from multiple vendors. By leveraging OCP’s existing Open Chiplet Economy initiative, contributors can ensure alignment with ongoing work on packaging, testing, and design-exchange standards, which accelerates innovation while minimizing risk and redundancy.

Charting the path to the converged AI data center

The Foundation Chiplet System Architecture is more than a specification; it’s a shared foundation for the next era of silicon design. By aligning open standards for interoperability, Arm and OCP are enabling the industry to transition from proprietary multi-die systems to an open, standards-driven ecosystem, where full system co-design is essential, such as in the AI-defined vehicle in the automotive sector.

Get involved in building an Open Chiplet Economy

- Join the FCSA workstream – Review the first draft of FCSA 1.0. Contribute to FCSA by participating in the new FCSA workstream at https://ocp-all.groups.io/g/ocp-fcsa and building on the FCSA and FCSA-aligned specification. Workstream calls are public meetings that take place via Zoom.

- More information https://www.opencompute.org/wiki/Server/OCE/FCSA

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Blogs

- Accelerating an Open Chiplet Ecosystem for Automotive with Foundation Chiplet System Architecture

- An Open Framework for exploring Architecture Interoperability driving multi-vendor Chiplet Eco-systems

- The IOHub. An Emerging Pattern for System Connectivity in Chiplet-Based Designs

- Addressing the Colossal Challenge of System Co-Optimization with a Holistic Chiplet Design Methodology

Latest Blogs

- Ultra-high repeatability and ultra-low insertion loss wafer and die-level visible-range E-PIC device characterization using an MPI Corp. probe system, enabled by process optimization from Quantum Transistors

- The Changing ASICs Landscape: the Shift Toward Chip Disaggregation

- Topology and Data Movement in Multi-Die Design

- How to Streamline Your Advanced Package (Chiplet, 3DIC) Interconnect Designs

- Interface IP: The Keystone for 3D Multi-Die Designs