Bridging the Gap to Chiplet Interoperability

The move to multi-die integration brings both promise and complexity. Scalable interconnects and automation are emerging as key enablers of future designs.

Chiplets have emerged as a dominant theme in discussions of next-generation system architectures. The current narrative describes a vision where design teams can mix and match dies from different sources, using standard interfaces and simplified flows to build multi-die systems.

Chiplets have emerged as a dominant theme in discussions of next-generation system architectures. The current narrative describes a vision where design teams can mix and match dies from different sources, using standard interfaces and simplified flows to build multi-die systems.

The analogy to off-the-shelf IP components is often cited, with chiplets expected to become as accessible and interoperable as passives or even microcontrollers. However, while compelling, this narrative is still a long way from reality.

The Current Landscape of Chiplet Integration

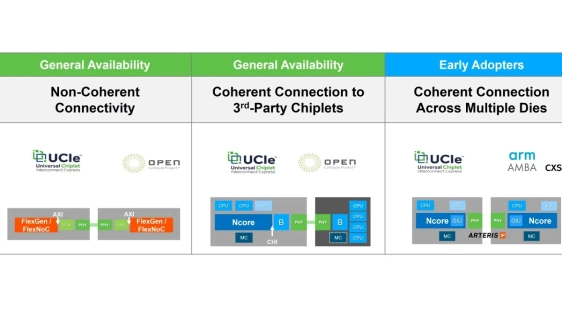

Chiplets typically fall into two architectural categories: homogeneous scale-out and heterogeneous disaggregation. Homogeneous designs use multiple identical dies within a package to expand performance capacity, while heterogeneous approaches combine functionally distinct dies tailored to specific roles.

To read the full article on Electronic Design, click here.

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Blogs

- UMI: Extending Chiplet Interconnect Standards To Deal With The Memory Wall

- Embracing the Chiplet Journey: The Shift to Chiplet-Based Architectures

- Introduction to Chiplets: Why the Industry is Moving Beyond Monolithic Designs

- Automotive chiplets: The path towards modularity, improved cost structures and supply resilience

Latest Blogs

- Wafer-Scale vs. Chiplets: The new war?

- Chiplets 101: An Arteris Guide to Multi-Die Architecture

- 2.5D + 3D = “3.5D”!

- Addressing AI and Advanced Packaging Challenges with Synopsys 3DIO PHY

- Ultra-high repeatability and ultra-low insertion loss wafer and die-level visible-range E-PIC device characterization using an MPI Corp. probe system, enabled by process optimization from Quantum Transistors