System-Level Validation Across Multiple Platforms to build a Robust 2.5D Multi Foundry Chiplet Solution

By Srivatsa Rangachar Srinivasa, Dileep Kurian, Paolo Aseron, Prerna Budhkar, Vinayak Honkote, Dan Lake, Jaykant Timbadiya, Satish Yada, Suresh Kadavakollu, James Greensky, Gauthaman Murali, Anuradha Srinivasan, Ragh Kuttappa, Tanay Karnik

Intel

Abstract

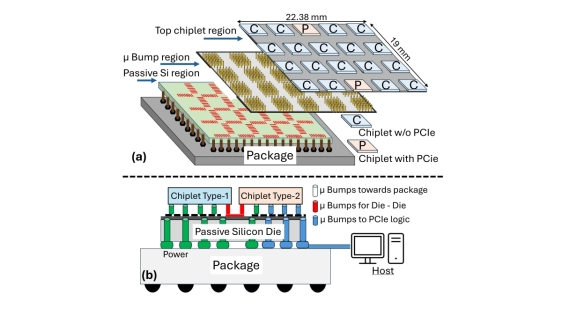

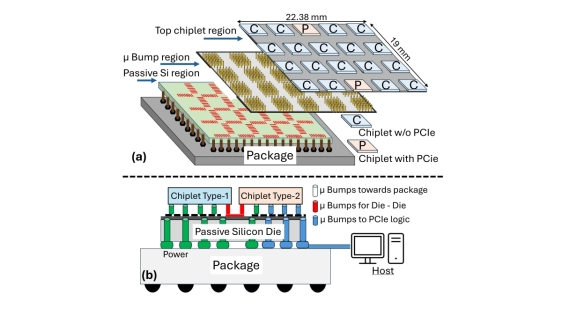

The proliferation of chiplet-based designs, driven by the escalating computational demands of AI, presents unique validation challenges when integrating heterogenous chiplets. This paper investigates the complexities of realizing large-scale chiplet systems with passive silicon base scaling beyond multi-reticle approaches, particularly addressing the heterogeneity introduced by varying functionalities with diverse manufacturing origins (multiple foundries). We propose three distinct validation platforms: hardware-aware software enablement, FPGA-based prototyping for seamless hardware porting, and specialized infrastructure for silicon system measurement, to optimize system efficiency. These platforms provide a structured framework for validating and deploying complex chiplet heterogenous architectures, exemplified by our target 20-chiplet System-In-Package (SIP). We demonstrate mapping workloads onto the hashing accelerator following the proposed approach to obtain speed up between 4x – 5x compared against CPU.

The proliferation of chiplet-based designs, driven by the escalating computational demands of AI, presents unique validation challenges when integrating heterogenous chiplets. This paper investigates the complexities of realizing large-scale chiplet systems with passive silicon base scaling beyond multi-reticle approaches, particularly addressing the heterogeneity introduced by varying functionalities with diverse manufacturing origins (multiple foundries). We propose three distinct validation platforms: hardware-aware software enablement, FPGA-based prototyping for seamless hardware porting, and specialized infrastructure for silicon system measurement, to optimize system efficiency. These platforms provide a structured framework for validating and deploying complex chiplet heterogenous architectures, exemplified by our target 20-chiplet System-In-Package (SIP). We demonstrate mapping workloads onto the hashing accelerator following the proposed approach to obtain speed up between 4x – 5x compared against CPU.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Automakers And Industry Need Specific, Extremely Robust, Heterogeneously Integrated Chiplet Solutions

- Towards Future Microsystems: Dynamic Validation and Simulation in Chiplet Architectures

- TDPNavigator-Placer: Thermal- and Wirelength-Aware Chiplet Placement in 2.5D Systems Through Multi-Agent Reinforcement Learning

- NoCs and the transition to multi-die systems using chiplets

Latest Technical Papers

- Spatiotemporal thermal characterization for 3D stacked chiplet systems based on transient thermal simulation

- Interconnect-Aware Logic Resynthesis for Multi-Die FPGAs

- Scope: A Scalable Merged Pipeline Framework for Multi-Chip-Module NN Accelerators

- Scaling Routers with In-Package Optics and High-Bandwidth Memories

- TDPNavigator-Placer: Thermal- and Wirelength-Aware Chiplet Placement in 2.5D Systems Through Multi-Agent Reinforcement Learning