OPENEDGES Unveils UCIe Chiplet Controller IP, Expanding Design Portfolio

Seoul, South Korea, Aug 13th, 2024 --- OPENEDGES Technology, Inc. (OPENEDGES), the leading provider of memory subsystem intellectual property (IP), today announced the launch of the Universal Chiplet Interconnect Express (UCIe) Controller IP, named OUC. UCIe is an open industry standard for a die-to-die interconnect, and co-developed by industry giants including AMD, Arm, ASE Group, Google Cloud, Intel, Meta, Microsoft, Qualcomm, Samsung, and TSMC. UCIe is becoming a new trend in the semiconductor industry due to its advantages, such as increased semiconductor circuit integration, reduced production costs, and higher yields. OPENEDGES is contributing to UCIe consortium as a contributing member.

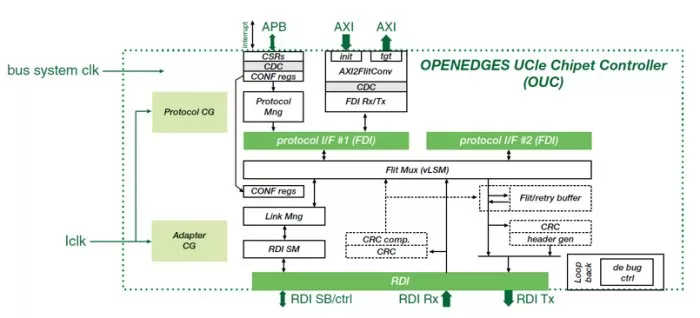

The OUC, deriving its name from OPENEDGES UCIe Controller, is tailored for highly customizable, package-level integration, facilitating die-to-die interconnect and protocol connections. It creates an interoperable, multi-vendor ecosystem set to revolutionize chip integration methodologies across the industry.

<Image 1: OPENEDGES UCIe Chiplet Controller (OUC) Block Diagram>

Leveraging OPENEDGES’ extensive expertise in interconnect IP development, the OUC is a versatile and highly configurable die-to-die controller that complies with the UCIe 1.1 standard. It extends on-chip AXI interconnections to multi-die connections, delivering an advanced solution for multi-die connectivity across diverse applications. The controller utilizes flits (flow control units) optimized for reliability and latency, preventing overflow at the receiver buffer. Furthermore, the OUC ensures seamless communication by synchronizing AXI parameters with its link partner, accommodating different AXI configurations through padding and cropping as per the default operation rules defined in AXI.

Designed for seamless multi-die communication, the OUC effortlessly integrates with OPENEDGES’ on-chip interconnect IP, OIC. This synergy between OIC and OUC simplifies the extension of on-chip interconnects to form multi-chiplet interconnects, utilizing OIC’s ActiveQoS and efficient bandwidth transfer capabilities to meet the complex demands of today’s semiconductor needs.

<Image 2: Ethan Hyun-Gyu Kim, team leader of Interconnect and UCIe chiplet controller IPs>

“Using our extensive experience with the development of interconnect IP, we were able to achieve development milestones more quickly,” said Ethan Hyun-Gyu Kim, the team leader of Interconnect and UCIe Chiplet Controller IP. “It is our intention to continually optimize our products in accordance with the evolving chiplet standards, and to actively assist our clients in ensuring their chips are successfully mass produced.”

“As chip complexity increases with advanced integration, the demand for UCIe is steadily growing” said Sean Lee, CEO of OPENEDGES Technology. “OPENEDGES will continue to provide a competitive and diverse IP portfolio, following our offerings in memory subsystem and NPU IP. We will not only adapt the industry trends but define them, providing our clients with the tools to build the technological landscapes of the future.”

This accomplishment was supported by Institute of Information & communications Technology Planning & Evaluation (IITP) grant funded by the Korea government (MSIT) (RS-2023-00222171, Development of Tbps/mm interface IP and Silicon Photonics Application Technology for AI and Automotive SoC Chiplet Interfaces).

About OPENEDGES Technology, Inc.

OPENEDGES Technology, Inc. is a premier provider of memory subsystem IPs for the semiconductor industry. They offer a wide range of state-of-the-art solutions, including DDR memory controllers, DDR PHY, NoC interconnect, and NPU IPs that are widely adopted by customers worldwide. Their IPs comply with JEDEC standards, including LPDDR5x/5/4x/4/3, DDR5/4/3, GDDR6, and HBM3, ensuring their compatibility with the latest DDR technology trends. In 2019, they acquired The Six Semiconductor, Inc. (TSS), specializing in high-speed memory PHYs across multiple technologies. In 2021, the company established a subsidiary in the USA, followed by another in Japan in 2024, further expanding their global footprint. Additionally, ISO9001:2015 certification was achieved early this year, highlighting their commitment to quality management, and is currently undergoing the certification process for ISO26262 Automotive Safety Integrity Level (ASIL). As a publicly listed company on the Korean Stock Exchange Market (394280. KQ), OPENEDGES is well-positioned to continue its growth and maintain its leadership in the memory subsystem IPs market.

Learn more about the company and its offerings by visiting the official website at www.openedges.com.

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- Alphawave Semi Taped-Out Industry Leading 64Gbps UCIe™ IP on TSMC 3nm for the IP Ecosystem, Unleashing Next Generation of AI Chiplet Connectivity

- Alphawave Semi Delivers Cutting-Edge UCIe™ Chiplet IP on TSMC 3DFabric® Platform

- GUC Taped Out UCIe 32G IP using TSMC's 3nm and CoWoS Technology

- System-level UCIe IP for early architecture analysis of 3D Chiplet Design and Packaging

Latest News

- Lightmatter Achieves Record 1.6 Tbps Per Fiber to Accelerate AI Optical Interconnect

- Arm Positions Neoverse for AI and Telco Networks at MWC

- NVIDIA Compute Architecture Paves the Way for Scale-Up Optical Interconnects; CPO Penetration in AI Data Centers Expected to Rise Steadily

- CEA-Leti and NcodiN Partner to Industrialize 300 mm Silicon Photonics for Bandwidth-Hungry AI Interconnects

- HyperLight, UMC, and Wavetek Announce Strategic Partnership for High-Volume Foundry Production of TFLN Chiplet™ Platform