MZ Technologies Unveils Next Generation Chiplet/Package Design Tool

ROME, Jan. 14, 2025 -- MZ Technologies, a leading supplier of innovative solutions and methodologies for 2.5 and 3D design, today unveiled GENIO EVO, the first integrated chiplet/package EDA tool to address in pre-layout stage the two major issues of 3D-IC design, thermal and mechanical stress. MZ will demonstrate this new tool at the Chiplet Summit, being held from January 21-23, 2025 at the Santa Clara Convention Center.

GENIO EVO is the second generation of GENIO™, which was the EDA's first successful integrated chiplet/package co-design tool. GENIO, MZ's flagship product, is a cross-fabric platform for system design providing chiplet/die, silicon interposer, package, and surrounding PCB co-design features that achieve area, power, and performance targets. The tool is technology agnostic and seamlessly integrates through standard formats with all the existing commercial implementation platforms or to custom EDA flows through dedicated plug-ins.

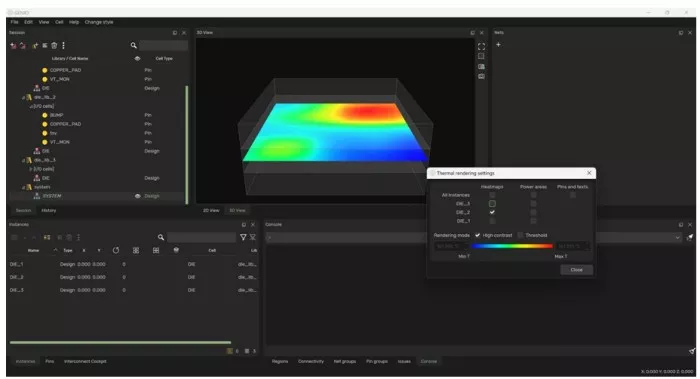

The new GENIO EVO graphic user interface provides a very detailed thermal analysis rendering.

Like the original, GENIO EVO fits into any existing design flow and operates at the architecture level, pathfinding the optimal system choices to implement a 2.5D or 3D multi-die design.

A new user interface fronts a cross-hierarchical, 3D-aware design methodology that streamlines the entire system design process. IC and advanced packaging design are integrated to ensure full system level optimization, with a shorter design cycle, faster time-to-manufacturing, and improved yields.

GENIO EVO provides additional identification and analysis of thermal and mechanical failures. It promotes architectural exploration and what-if analysis during early stages of design to improve predictability during implementation. It anticipates and avoid downstream thermal and mechanical issues by planning & managing high pin count interconnect in complex multi-fabric system design.

Aside from its design capabilities, GENIO EVO improves cross-team communications because components of any nature can be imported from different design environment.

Barriers to Innovation

In 3D-packaged heterogeneous semiconductor devices, thermal stress arises from uneven heat distribution during operation, potentially leading to warping and reliability failures. Effective thermal management strategies are essential to minimize temperature differentials, ensuring optimal performance and longevity of the integrated chiplets within the package.

Mechanical stress in 3D-packaged designs can result from factors such as thermal expansion mismatch and substrate flexing. These stresses can cause interconnect failures or delamination. A robust design framework must address these challenges to maintain structural integrity and performance across varying operational conditions and material interfaces.

"MZ Technologies was the first EDA company to deliver a commercially available co-design tool three years ago and now GENIO EVO is first tool to successfully anticipate and fix mechanical and thermal failures prior to design iteration," said Anna Fontanelli, founder and CEO of MZ Technologies.

GENIO EVO is available for immediate licensing.

For a more information, go to www.monozukuri.eu

About MZ Technologies

MZ Technologies is the marketing function of Monozukuri S.p.A. Monozukuri's mission is to conquer 2.5D & 3D design challenges for next generation electronic products by delivering innovative, ground-breaking EDA software solutions and methodologies. The technology redefines the co-design of heterogeneous microelectronic systems by providing an improved level of automation in three-dimensional interconnect optimization.

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- MZ Technologies unveils roadmap for its integrated chiplet/packaging Co-Design EDA tool

- Alchip Unveils AI 3DIC Design and IP Platform

- SEMIFIVE Signs MOU with Atron Technologies to Collaborate on Semiconductor Design

- U.S. Navy Funds Mercury to Advance Chip-Scale Technologies Needed to Reduce Electronic Warfare Design Timelines

Latest News

- Athos Scraps Multi-Vendor Roadmap, Plans Chiplet Tape-Out

- LTSCT Joins imec Automotive Chiplet Program

- CEA-Leti Will Present Its Latest Advances On Next-Generation Chip Integration at ECTC 2026

- OpenLight Secures $50 Million in Series A-1 Funding to Accelerate Global Deployment of Next-Generation Photonics

- Lightmatter Names Roy Kim Vice President of Product to Lead Global Deployment of Photonic Interconnects