UCIe Manageability: The Hidden Control Plane of Chiplet Systems

Chiplet-based architectures are quickly becoming the foundation of next-generation silicon systems. While most attention goes to high-bandwidth die-to-die links and data protocols like PCIe or CXL, an equally important layer operates quietly in the background: System Manageability.

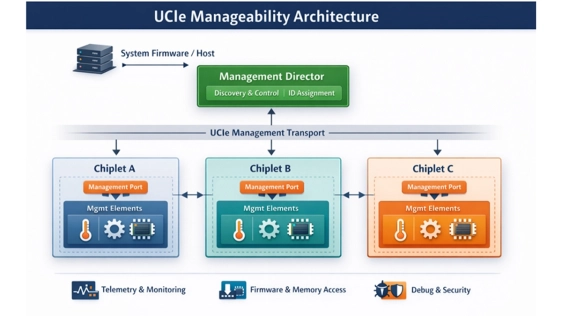

Section 8 of the Universal Chiplet Interconnect Express (UCIe) Specification introduces the manageability architecture, which defines a standardized framework for discovering, configuring, and controlling chiplets inside a System-in-Package (SiP).

Section 8 of the Universal Chiplet Interconnect Express (UCIe) Specification introduces the manageability architecture, which defines a standardized framework for discovering, configuring, and controlling chiplets inside a System-in-Package (SiP).

For system architects and verification engineers, this layer effectively functions as the control plane of a chiplet system, enabling firmware, debug tools, and system software to interact with chiplets using a consistent management infrastructure.

Why Manageability Matters in Chiplet Systems

Unlike monolithic SoCs, chiplet-based systems often integrate dies from multiple vendors, each with different internal architectures. Without a common management framework, system-level operations such as configuration, monitoring, and debug would require vendor-specific solutions, complicating system integration.

UCIe manageability addresses this by defining a management network spanning all chiplets within the package. Through this network, system firmware can perform essential operations including:

- Chiplet discovery during system initialization

- Chiplet ID assignment and topology configuration

- Remote register access and telemetry collection

- Firmware loading and system configuration

- Debug and diagnostic access

- Security configuration

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Blogs

- Cadence Sets the Gold Standard for UCIe Connectivity at Chiplet Summit '24

- UCIe and Automotive Electronics: Pioneering the Chiplet Revolution

- The Impact of UCIe on Chiplet Design: Lowering Barriers and Driving Innovation

- The Growing Chiplet Ecosystem: Collaboration, Innovation, and the Next Wave of UCIe Adoption

Latest Blogs

- Wafer-Scale vs. Chiplets: The new war?

- Chiplets 101: An Arteris Guide to Multi-Die Architecture

- 2.5D + 3D = “3.5D”!

- Addressing AI and Advanced Packaging Challenges with Synopsys 3DIO PHY

- Ultra-high repeatability and ultra-low insertion loss wafer and die-level visible-range E-PIC device characterization using an MPI Corp. probe system, enabled by process optimization from Quantum Transistors