Chiplets Have Become Essential in a Post-Moore's Law World

For a generation of engineers, Moore’s law has proved to be a constant. The industry has continued to advance forward year after year with the promise of performance gains holding steady. That is until recently. With Moore’s law at least slowing (if not outright failing) and Dennard Scaling also long over, the era of guaranteed performance gains has come to an end. With the shift toward a more vertically integrated approach from most of the fabless players, the question of what to do in a post-Moore’s law world is one that needs solving.

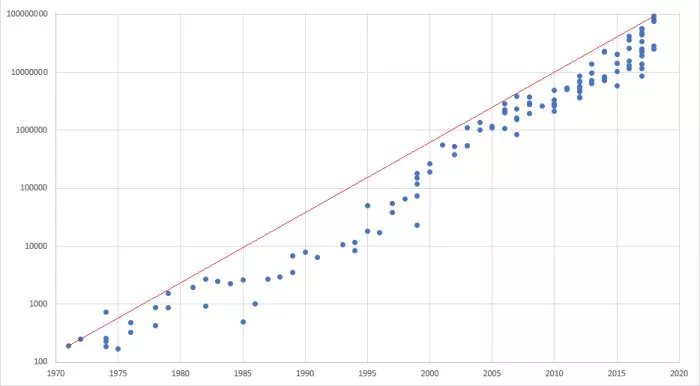

Moore's Law (till 2020)

The Challenges Beyond Moore’s Law

As we’ve pushed transistors to their smallest possible size, we’re facing three big issues:

- Physical Limits: Chips are now so small – down to 2 nm process nodes that the physical limit of shrinking sizes is going to be reached.

- Cost: Designing chips at the leading transistor nodes has become prohibitively expensive.

- Diminishing returns: Smaller doesn’t always mean better anymore. The performance gains from designing on the latest process nodes are no longer proportional to the effort and cost involved.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Blogs

- Functional Safety in a Disaggregated World

- The Role of Chiplets in Semiconductor Design: A Modular Approach

- Four Reasons Chiplets Will Take Over the World (and why it hasn’t happened yet)

- Integrated Design Ecosystem™ for Chiplets and Heterogeneous Integration in Advanced Packaging Technology

Latest Blogs

- Wafer-Scale vs. Chiplets: The new war?

- Chiplets 101: An Arteris Guide to Multi-Die Architecture

- 2.5D + 3D = “3.5D”!

- Addressing AI and Advanced Packaging Challenges with Synopsys 3DIO PHY

- Ultra-high repeatability and ultra-low insertion loss wafer and die-level visible-range E-PIC device characterization using an MPI Corp. probe system, enabled by process optimization from Quantum Transistors