創意電子為 AI/HPC/網路產業客戶提供完整的3DIC ASIC 套裝服務

2024 年 4 月 18 日台灣新竹 – 先進特殊應用積體電路 (ASIC) 領導廠商創意電子 (GUC) 今日宣佈,專為台積電 3DFabric SoIC-X 3D 堆疊平台打造的 GLink-3D 介面 (GUC 的 3D 晶粒堆疊連結) 已通過了全面的晶片測試,驗證了 3DIC 介面hardening流程。旗下的首個 GUC 3D 客戶專案,也通過了完整的矽測試,驗證了 AI/HPC/網路應用的全方位 3D 實作服務。

典型的 AI/HPC/網路晶片結合大型記憶體和高效能邏輯。遷移邏輯單元至最先進的製程可為邏輯單元帶來功耗、速度和尺寸方面的提升,相較之下,遷移 SRAM 至最先進的製程則不會帶來顯著的效益。將先進製程節點中的邏輯小晶片堆疊在具 SRAM 遷移效率且較低階節點內以 SRAM 為主的小晶片上,將可造就最具性價比的解決方案。兼具高頻寬、低延遲和低功耗等特點的 GLink-3D 介面 IP,為促成此一解決方案的一大助力。而其他有待因應的挑戰,則包含 3D 堆疊小晶片的散熱和配電。創意電子精心開發出完整的 3D 設計流程,並實作了首位客戶於記憶體上配置邏輯的 3D 堆疊產品,而該產品已成功通過矽驗證。當中採用的矽相關設計和模擬流程,可使用新興的 UCIe-3D 介面標準來順暢完成實作。

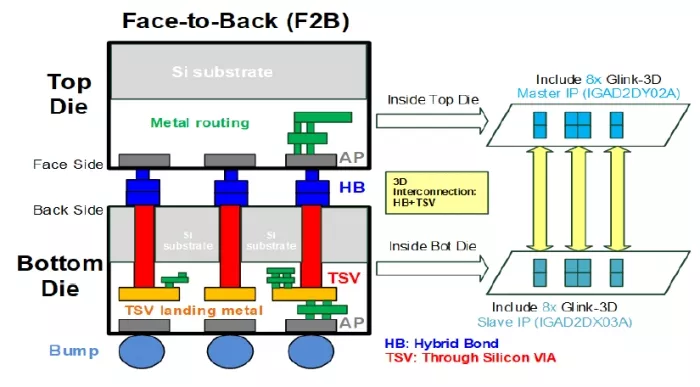

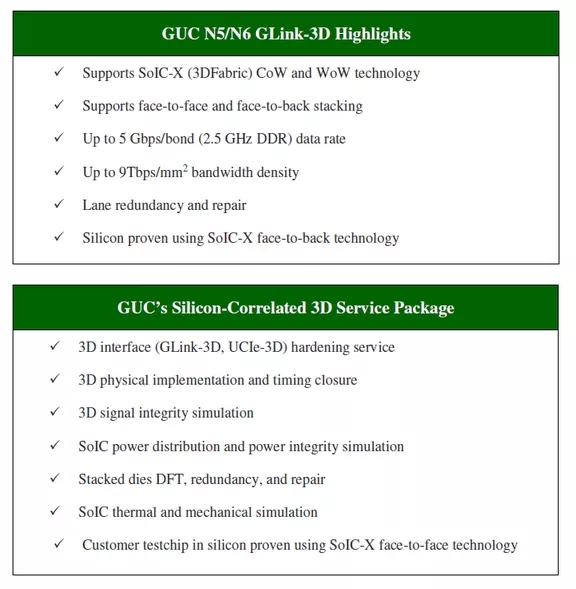

為了滿足最高等級的 3D 介面頻寬密度需求,創意電子開發出採用雙倍資料速率 (DDR) 和自適應時序架構的 GLink-3D 介面。這款模組化解決方案具有足夠的彈性,可支援使用者的匯流排和時脈機制,在避免跨晶粒/Corner時序收斂挑戰的同時,提供 9 Tbps/mm2 的頻寬密度。GLink-3D 使用 TSMC 旗下第一款在 N6 SRAM 堆疊晶粒上配置 N5 CPU 邏輯的 SoIC-X 測試晶片來完成驗證。在 IP 穩健度方面,所有製程、電壓與溫度條件範圍皆已進行驗證,可提供 BER <1E-30、高供電電壓和頻率裕度,以及強大的供電雜訊抗擾性。目前,創意電子也在開發適用於 N2 至 N7 的新一代 GLink-3D,並以 20 至 40 Tbps/mm2、0.2 ns 至 0.6 ns 延遲性和 UCIe-3D 合規性做為目標。

Figure 1. Multiple GLink-3D IPs were implemented in both dies of the SoIC-X testchip:

創意電子行銷長 Aditya Raina 表示:「3D 封裝技術可將小晶片介面從晶粒邊緣移至位於小晶片中任一處的最佳位置,以盡可能縮短邏輯和記憶體之間的互連。創意電子將結合自身的 CoWoS®、InFO 和 SoIC 設計專業能力、封裝設計、電氣和熱模擬,以及 DFT 與生產測試能力,為客戶提供穩健且全方位的解決方案,協助他們縮短設計週期,快速推出 AI/HPC/xPU/網路等產品。」

創意電子技術長 Igor Elkanovich 表示:「3D 技術可讓系統結合強大的處理能力和大量的記憶體,並在效率最高的製程節點中建立每個元件。我們精心開發且通過矽驗證的 3D 介面 (GLink-3D) hardening服務、3D 實體實作和時序收斂、訊號完整性、電源分配和電源完整性,以及 SoIC 熱模擬和機械模擬,將可提供完整的套裝服務,以協助旗下的客戶專案降低採用 3D 技術的風險。」

若要進一步了解相關資訊,請直接聯絡您的創意電子銷售代表,或是寄送電子郵件,請至:guc_sales@guc-asic.com

Related Chiplet

- Interconnect Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Bridglets

- Automotive AI Accelerator

- Direct Chiplet Interface

Related News

- Chiplets的2.5D/3D先进封装服务

- 领先的半导体厂商、封装商、IP供应商、晶圆代工厂和云服务提供商联合制定小芯片生态系统标准

- nepes采用西门子EDA先进设计流程,扩展3D 封装能力

- 西门子推出Calibre 3DThermal 软件,持续布局3D IC市场