Shin-Etsu Chemical: Developing equipment to manufacture semiconductor package substrates for the back end process and pursuing a new manufacturing method

Contributing to the cost reduction of ongoing chiplet development

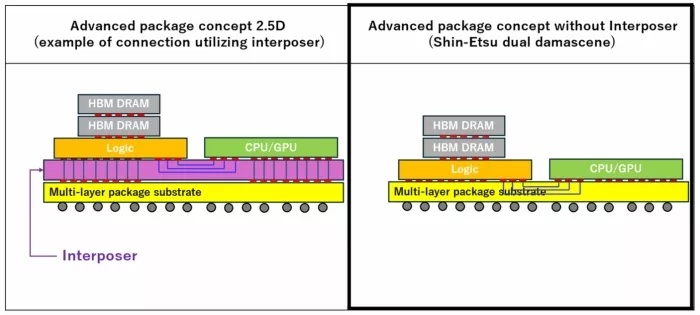

June 12, 2024 -- Shin-Etsu Chemical Co., Ltd. (Head Office: Tokyo; President: Yasuhiko Saitoh; hereinafter, “Shin-Etsu Chemical”) has developed equipment to manufacture semiconductor package substrates with a new manufacturing method subsequently to manufacturing micro-LED manufacturing system. The equipment is a high-performance processing equipment using excimer laser in which a dual damascene method, as is also used in the front end of semi-conductor manufacturing process, is applied to package substrate manufacturing process (back end process) (Shin-Etsu dual damascene method). As a result, an interposer’s functions directly formed into a package substrate. This not only eliminates the need of an interposer, but also enables further microfabrication, where conventional manufacturing methods could not realize. It also reduces costs and capital investment as it does not require the photoresist process in package substrate manufacturing process.

A chiplet, in which circuits are singulated and then assembled in a package, has caught attention as a technology to reduce the manufacturing cost of higher-performance semiconductors. This technology requires a process to mount several chiplets on an intermediate substrate and connect them. The intermediate substrate is called an “interposer.”

With the Shin-Etsu dual damascene method, interposer is not necessary any more, so it significantly simplifies the assembly process. In this method, chiplets are connected to a package substrate with wiring patterns which has equivalent function to an interposer. Consequently, the assembly process of advanced semiconductors with chiplet technology can be shortened and its cost can be drastically reduced.

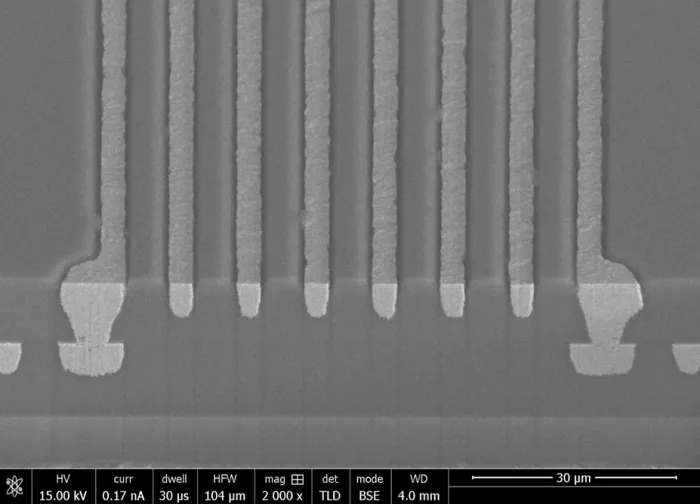

The equipment’s sophisticated microfabrication technology allows complicated electric circuit patterns to be formed directly in each organic insulation layers of a multi-layered package substrate, followed by circuit forming by copper plating. It uses an excimer laser as a light source to form large-area electric circuit patterns in batches. The Shin-Etsu dual damascene method enables further miniaturized microfabrication, which could not be achieved by semi-additive processing (SAP) method using dry film resist, as is current mainstream. The laser processing equipment can process an area of 100 mm square or larger at one time with a combination of a photomask made of Shin-Etsu’s large photomask blanks and its unique special lens. Processing time varies depending on the size of one package substrate, but the time required to process the wiring pattern and electrode pads is the same as the time required to process vias. Moreover, the via processing time does not depend on the number of vias. For example, it takes about 20 minutes to form trenches of 2 µm width and 5 µm depth and electrode pads of 10 µm diameter and 5 µm depth on an organic substrate of 515 mm × 510 mm, as well as to form vias (upper diameter 7 µm, lower diameter 5 µm, depth 5 µm).

Shin-Etsu Chemical is working on initiatives to integrate its own material and equipment technologies. By developing new process technology, we will propose total solutions from the perspectives of both equipment and materials and take the lead in the development of next-generation technologies to create an affluent society.

Two-layer sample processed by Shin-Etsu dual damascene method (Overhead view)

Two-layer sample processed by Shin-Etsu dual damascene method (Cross-section view)

Advanced package concept proposed by Shin-Etsu Chemical

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- NHanced Semiconductors Opens Leading-Edge Advanced Package Assembly Facility, Reinforcing Indiana’s Position as a Major Semiconductor Hub

- Samsung Electronics To Provide Turnkey Semiconductor Solutions With 2nm GAA process and 2.5D Package to Preferred Networks

- Opportunities Unleashed by Chiplet Technology: A New Era for the Semiconductor Industry

- DreamBig Semiconductor Announces Partnership with Samsung Foundry to Launch Chiplets for World Leading MARS Chiplet Platform on 4nm FinFET Process Technology Featuring 3D HBM Integration to Solve Scale-up and Scale-out Limitations of AI for the Masses

Latest News

- TIER IV joins imec’s Automotive Chiplet Program to accelerate chiplet-based architectures and AI accelerators for SDVs

- Adeia Enters into Multi-Year IP License Agreement with AMD

- STMicroelectronics enters high-volume production of its industry-leading silicon photonics platform to support AI infrastructure demand

- Vertical Compute raises €57M to solve the AI memory bottleneck with new high density memory

- Ayar Labs Closes $500M Series E, Accelerates Volume Production of Co-Packaged Optics