Nvidia, TSMC, and advanced packaging realignment in 2025

By Majeed Ahmad, EDN (January 20, 2025)

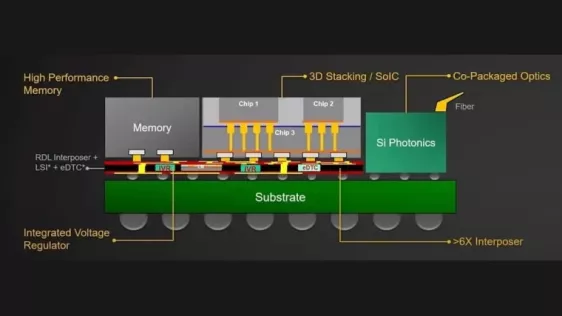

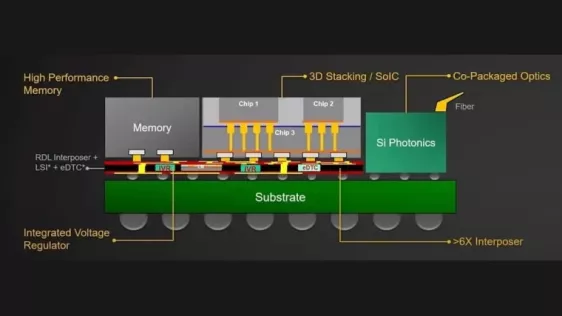

Nvidia’s CEO Jensen Huang has made waves by saying that his company’s most advanced artificial intelligence (AI) chip, Blackwell, will transition from CowoS-S to CoWoS-L advanced packaging technology. That also shows how TSMC’s advanced packaging technology—chip on wafer on substrate (CoWoS)—is evolving to overcome interconnect battles inside large, powerful chips for AI and other high-performance computing (HPC) applications.

Nvidia’s CEO Jensen Huang has made waves by saying that his company’s most advanced artificial intelligence (AI) chip, Blackwell, will transition from CowoS-S to CoWoS-L advanced packaging technology. That also shows how TSMC’s advanced packaging technology—chip on wafer on substrate (CoWoS)—is evolving to overcome interconnect battles inside large, powerful chips for AI and other high-performance computing (HPC) applications.

The CoWoS-S advanced packaging technology uses a single silicon interposer and through-silicon vias (TSVs) to facilitate the direct transmission of high-speed electrical signals between the die and the substrate. However, single silicon interposers often confront yield issues.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- Amkor and TSMC to Expand Partnership and Collaborate on Advanced Packaging in Arizona

- Lorentz Solution Jointly Presents with NVIDIA on Large-Scale 3D Terahertz EM Simulation for Real IC/3DIC Silicon Case Studies in Photonic Switches at 2025 TSMC OIP

- JCET Accelerates Strategic Shift Toward High-End Advanced Packaging, 2025 Advanced Packaging Revenue Hits Record High

- IC-Link by imec joins TSMC 3DFabric® Alliance to accelerate advanced packaging and 3D IC innovation

Latest News

- Tower Semiconductor Signs Customer Contracts for $1.3 Billion Silicon Photonics Revenue for 2027

- IC-Link by imec joins TSMC 3DFabric® Alliance to accelerate advanced packaging and 3D IC innovation

- EXTOLL announces Availability of Industry's first 16G UCIe PHY IP in GlobalFoundries 22FDX/22FDX+ Ready for Customer Integration

- NHanced Semiconductors & the University of Florida to Present on Hybrid Bonding Reliability at the 2026 Electronic Components & Technology Conference in Orlando

- Wooptix Targets AI Packaging Bottleneck with Astronomy Tech