CoAsia SEMI Announces AI Chiplet Production Collaboration With Tenstorrent

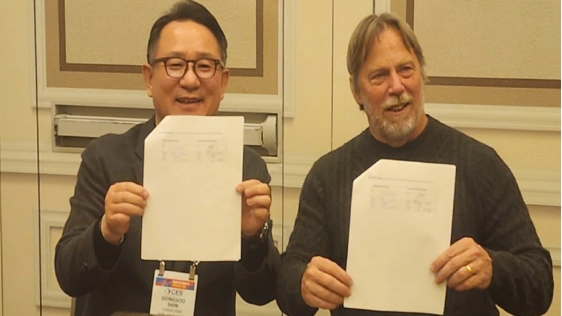

January 12, 2026 -- CoAsia SEMI announced its production collaboration with Tenstorrent, a global AI semiconductor company, during CES 2026 in Las Vegas.

The collaboration builds on an existing chiplet development engagement between the two companies and supports the transition of select AI chiplet programs from development into production readiness. The agreement reflects continued progress following the successful completion of key design milestones.

The collaboration builds on an existing chiplet development engagement between the two companies and supports the transition of select AI chiplet programs from development into production readiness. The agreement reflects continued progress following the successful completion of key design milestones.

CoAsia SEMI independently estimates that, based solely on its internal projections, it may generate more than 140 billion KRW in revenue over the next five years under this collaboration.

Under this collaboration, CoAsia SEMI will provide chiplet implementation and production support services, including design enablement, verification support, and coordination across the manufacturing and packaging flow in alignment with Tenstorrent program requirements and schedules.

Keith Witek, COO of Tenstorrent, said, “CoAsia Semi is a highly trusted partner for implementing Tenstorrent’s chiplet-based SoC solutions, and we plan to further expand our collaboration. Following this agreement, we expect to begin development of next-generation products in the near future.”

DS Shin, CEO of CoAsia Semi and Head of the Semiconductor Division at CoAsia Group(KOSDAQ: 045970, CEO Heejun Lee), commented, “This agreement demonstrates the maturity and competitiveness of CoAsia’s chip design and chiplet packaging capabilities. Building on this achievement, we aim to take a leading role in the global AI ASIC market.”

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- CoAsia SEMI and Rebellions Join Forces to Jointly Develop Next-Generation AI Chiplet Based on REBEL

- Alphawave Semi Highlights Why the Next Generation of AI Advances Demand Chiplet Architectures at EE Times: The Future of Chiplets

- Alphawave Semi Taped-Out Industry Leading 64Gbps UCIe™ IP on TSMC 3nm for the IP Ecosystem, Unleashing Next Generation of AI Chiplet Connectivity

- Alphawave Semi to Lead Chiplet Innovation, Showcase Advanced Technologies at Chiplet Summit

Latest News

- Tower Semiconductor Signs Customer Contracts for $1.3 Billion Silicon Photonics Revenue for 2027

- IC-Link by imec joins TSMC 3DFabric® Alliance to accelerate advanced packaging and 3D IC innovation

- EXTOLL announces Availability of Industry's first 16G UCIe PHY IP in GlobalFoundries 22FDX/22FDX+ Ready for Customer Integration

- NHanced Semiconductors & the University of Florida to Present on Hybrid Bonding Reliability at the 2026 Electronic Components & Technology Conference in Orlando

- Wooptix Targets AI Packaging Bottleneck with Astronomy Tech