芯动科技推出首款国产UCIe Chiplet解决方案,加速大模型芯片设计创新

2024-02-01 -- 大语言模型时代,先进工艺大型芯片设计实现难度和复杂度高,全流程交付成本大幅增加。在技术挑战、成本挑战、时间挑战等驱动下,先进工艺高密度Chiplet互联技术作为目前先进制程的重要替代解决方案,其经济价值和战略价值被寄予厚望,有利于降本增效并且高效灵活适应多样化的市场需求。作为在高速接口互连技术深耕18年的赋能者,芯动科技率先推出了国内首款兼容UCIe标准的Chiplet解决方案,支持Die to Die、Chip to Chip、Interposer以及系统级互联,已在硅基板、MCM封装基板、化合物基板以及PCB级等场景广泛量产应用。

Chiplet是一种芯片“模块化”设计方案,把SoC中的功能块进行拆分,再将不同工艺制程、不同性质的芯片整合在一起,通过二维芯片的堆叠、三维方向的连接,如同搭积木一样将逻辑单元芯粒、计算单元芯粒、存储单元芯粒和IO单元芯粒高效组合起来,集成一个更大的系统级芯片(SoC),该方案具有高带宽、低延时、低功耗,以及设计灵活、开发周期短、迭代速度快、成本低、良率高等一系列优越特性,已然成为大算力时代设计和系统企业应对芯片设计成本和复杂度提升、多样化创新需求以及迭代周期加快的最优选择。但由于Chiplet是一系列技术的综合,诸如芯片的设计、封装的设计和仿真、连接协议实现等等都非易事。

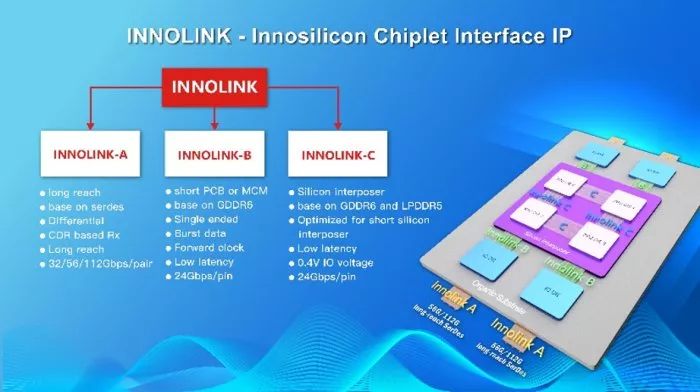

基于前期在DDR、SerDes等高速接口技术的自主创新和先进工艺的量产验证,集十多年IP前后端、工艺定制、封测量产全流程之经验能力,芯动科技在全球范围内率先推出了Innolink™ Chiplet互连解决方案,已经完成主流先进工艺silicon proven并在FPGA等平台上充分验证,在第三方产品以及芯动自研风华GPU等多个项目成功大规模量产。芯动科技IP研发副总裁高专介绍道,芯动在高速接口领域的技术优势由来已久,早在多年前就洞察技术趋势开始了Chiplet的研发工作,于四年前首发了Innolink™ Chiplet A/B/C三种技术路线。芯动Innolink™ Chiplet还前瞻性地与最新UCIe国际通用标准的技术路线保持一致,都是针对标准封装和先进封装单独定义IO接口,都是单端信号,forward clock、sideband通道、datavalid信号、burst数据、Idle低功耗等均方向一致。通过采用DDR模式,这种端到端连线可以直接通过GPIO在FPGA上进行互连,客户只需要调整频率就可以完成整个Chiplet在延迟总线、整体协议方面的全套仿真和验证工作。

芯动科技Innolink™ Chiplet还兼具高密度、低延迟、低功耗等特点,PPA优势明显,支持容错连接。Innolink-A是基于SerDes的互联技术,适用于较长的传输距离和较大信号衰减,可实现板卡到板卡之间的互连,支持32/56/112Gbps/pair传输速率。Innolink-B对应UCIe标准中的标准封装,基于DDR技术单端信号,可支持短距PCB和MCM,同时兼容Die to Die和Chip to Chip,最高支持24-28Gbps/pin传输速率。Innolink-C则对应UCIe标准中的先进封装,结合了GDDR和LPDDR的技术特点,针对2.5D和Silicon Interposer做了优化,IO电压可低至0.4V,最高支持24Gbps/pin传输速率。以上三种互联方案均已在多个客户产品中成功量产。

Innolink-B主要技术特点

- 兼容UCIe Standard Package

- 兼容传统flip chip封装

- Bump Pitch支持110um~180um可配置

- 整体GDS和bump布局全集成,Bump充分考虑封装走线实现和成本

- PHY和Controller整体解决方案,Controller支持多种上层总线接口

- 16Tx + 16Rx为一个module,可以多module扩展带宽

- 内置PLL和sideband信号

- 最高支持28Gbps/pin

Innolink-C主要技术特点

- 兼容UCIe Advanced Package

- 支持0.3V~0.5V IO电压

- Bump Pitch支持40um~80um可配置

- 整体GDS和bump布局全集成,Bump充分考虑封装走线实现和成本

- PHY和Controller整体解决方案,Controller支持多种上层总线接口

- 默认64Tx + 64Rx为一个module,可以多module扩展带宽

- 内置PLL和sideband信号

- 最高支持24Gbps/pin

芯动科技能推出业界领先的Chiplet解决方案,得益于两方面的基础。第一,芯动在4年前就在布局和研发基于单端信号的Chiplet技术,相应的技术在Design Reuse于2020年已经发布。这比UCIe早了2年多,比其它单端信号Chiplet技术vendor早了3年左右,所以芯动科技在UCIe类Chiplet技术有很大的先发优势。第二,UCIe类Chiplet技术使用的是类似DDR的高速单端信号,并且定义的最高单端信号速度为32Gbps,目前普遍的需求都是在16Gbps以上,单端信号速度达到16Gbps或者24Gbps以上,业界绝大部分企业没有类似技术经验,最快的DDR5或者LPDDR5也就6.4Gbps,24Gbps是6.4Gbps 速度的3.75倍,实现如此高单端信号的可靠传输,没有相应的技术基础和量产经验,显然是不太可能保证量产成功。芯动科技在2018年即实现了GDDR6 16Gbps的量产技术,而在单端高速IO技术上,GDDR6和UCIe有很多类似的底层技术。所以在单端高速IO技术实现上,芯动科技有独特的先天优势。这两点基础是全球其它友商所不具备的,也得益于这两个优势的加成,使得芯动的UCIe类Chiplet IP有显著的先发优势和技术优势,在赋能客户量产以及IP成熟度和多工艺布局上遥遥领先。

作为一家全栈式IP和芯片定制的赋能型企业,芯动科技一直为客户提供全套解决方案和差异化服务,提供在Fab的PDK规则下从RTL到门级电路、从验证模型到模拟电路、从前端设计到后端版图的实现,包括GDS版图交付等,个性化满足客户不同的设计和封装要求。提供差异化服务和定制化研发的过程中,芯动科技在跨介质、跨平台的连接技术上积累了深厚的工程实践经验。因此,在Chiplet领域,芯动不但提供多种互联方式,还提供大量互联的可定制化协议能力,并且已有大规模量产应用的成功经验能助力客户把芯片组合的风险降到最低。可提供物理层方案,客户自主构建协议层,也可提供PHY&Controller打包方案,这两种方案均已授权客户量产测试,支持跨工艺跨封装,提供封装设计、可靠性验证、信号完整性分析、DFT、热仿真、测试方案等全栈式服务。

芯动科技18年自研高端IP,拥有行业经验丰富的开发团队,具备精湛的技术迭代能力和前瞻的市场洞察力,能够根据客户需求,提供业内最全面的、通过各大晶圆厂产线验证的,在带宽、速率、稳定性、可靠性等方面遥遥领先的接口IP,时提供体系架构、总线/内核拼接、IP集成/SoC集成等全套高性能芯片定制量产服务。芯动拥有高速内存IP、高速数据通信类IP和高清多媒体混合电路IP等在内的完整IP生态,所有IP完全自主研发,提供PHY和Controller一站式交钥匙集成,PPA场景优化,已在全球各大代工厂55nm至3nm工艺节点完成验证并大规模量产,创造了200多次流片纪录,全球超过150亿颗高端SoC芯片背后有芯动技术。

面对新一轮的大模型技术浪潮,芯动科技将用Chiplet等优势大模型底层技术和GPU/NPU/DPU/CPU/AI等关键内核定制服务,结合大量先进工艺量产成功经验,一站式助力客户算力产品升级迭代,赋能万物互联新时代。

Related Chiplet

- Interconnect Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Bridglets

- Automotive AI Accelerator

- Direct Chiplet Interface

Related News

- 小芯片先驱 Eliyan公司加入 UCIe 和 JEDEC 联盟,拓展资深领导团队以加速突破性Die-to-Die互连方案的普及

- Alphawave Semi展示用於高性能人工智慧基礎設施的3nm經矽片驗證的24Gbps Universal Chiplet Express™ (UCIe™) 子系統

- OPENEDGES 推出 UCIe 小芯片控制器 IP,扩展产品组合

- 领先的半导体厂商、封装商、IP供应商、晶圆代工厂和云服务提供商联合制定小芯片生态系统标准