Alphawave Semi展示用於高性能人工智慧基礎設施的3nm經矽片驗證的24Gbps Universal Chiplet Express™ (UCIe™) 子系統

矽技術的成功推出將擴展融合小晶片的矽解決方案領先地位,以加速人工智慧連接與運算

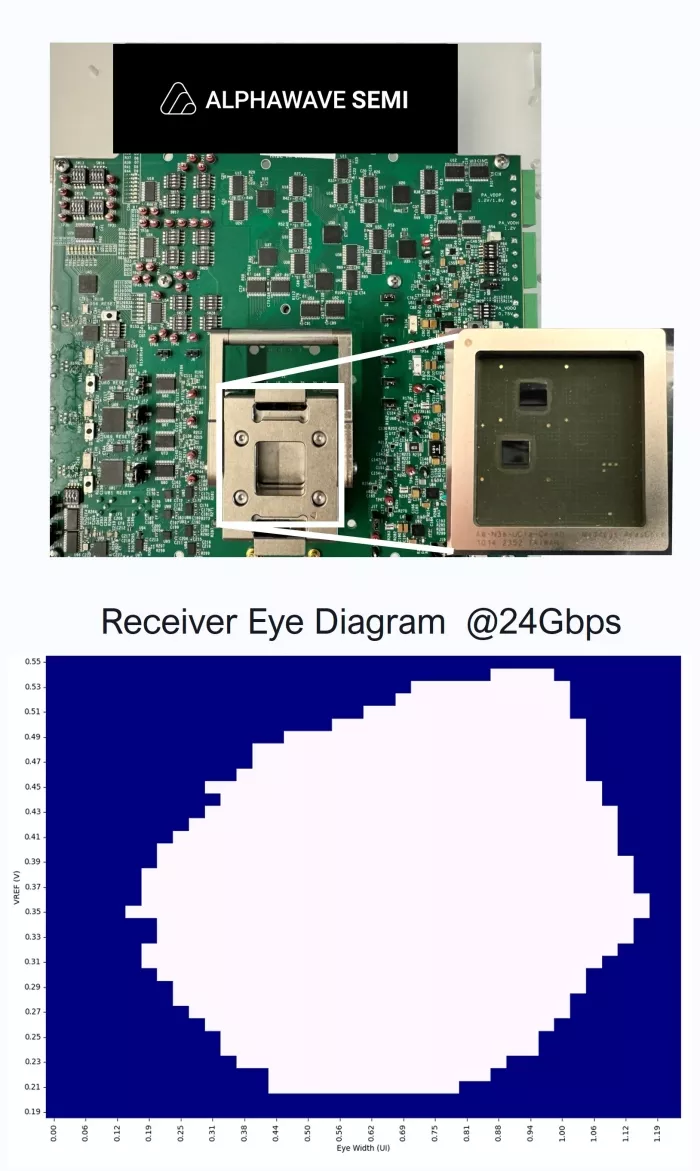

倫敦與多倫多-- 2024-03-13 -- 為全球技術基礎設施提供高速連接與運算解決方案的世界一流企業Alphawave Semi(倫敦股票交易所代碼: AWE)今天宣布成功推出首個採用台積電最先進的3nm製程的小晶片連接矽平台。這款經過矽驗證的新型Universal Chiplet Interconnect Express(UCIe™子系統擴展了Alphawave Semi在連接晶片方面的產品組合和領導地位。它為強大、開放的小晶片生態系統鋪平了道路,加速了高性能人工智慧系統的連接和計算。近日,在加州聖克拉拉舉行的Chiplet峰會上,Alphawave Semi採用台積電3nm工藝的24Gbps UCIe矽平台的現場示範在業界首次公布。

Alphawave Semi的3nm UCIe完整PHY +控制器子系統能夠實現24Gbps的數據速率,以極低功耗和低延遲提供高頻寬密度。該解決方案符合最新的UCIe 1.1版規範,並包括一個高度可配置的模對模D2D控制器,支持串流、PCIe® /CXL™、AXI-4、AXI-S、CXS及CHI協議。該子系統具有誤碼率(BER)狀態監測功能,以確保可靠運行。PHY可配置為支持台積電的先進封裝技術,如Chip-on-Wafer-on-Substrate(CoWoS®)和整合式扇出(InFO),最大限度提高信號密度及有機基板,以提供更具成本效益的解決方案。

台積電設計基礎設施管理部門主管Dan Kochpatcharin表示:「我們對與Alphawave Semi的最新合作成果感到滿意,雙方在台積電3nm工藝基礎上提供了經過矽驗證的小晶片連接解決方案。我們將繼續與開放創新平台(OIP)合作伙伴(如Alphawave Semi)合作,為高性能連接和計算晶片解決方案建立一個強大而開放的晶片生態系統,以實現更多的人工智慧應用。」

Alphawave Semi IP產品行銷副總裁Letizia Giuliano表示:「我們的24Gbps UCIe子系統實現3nm矽驗證狀態是Alphawave Semi的一個關鍵里程碑,因為它是我們為超大規模和數據基礎設施應用量身訂製的小晶片連接平台的重要組成部分。我們非常感謝台積電團隊的大力支持,我們期待著在台積電領先的3nm工藝基礎上為我們共同的客戶加速高性能晶片設計。」

更多資訊,請造訪:http://awavesemi.com。

透過將UCIe、PCIe、CXL、Multi-Standard-Serdes和HBM等先進介面整合到訂製晶片和小晶片上,客戶可受惠於Alphawave Semi的應用最佳化IP子系統和先進的2.5D/3D封裝專業知識。

關於 Alphawave Semi

Alphawave Semi 是全球技術基礎架構高速連接的世界領導者。面臨資料指數增長議題,Alphawave Semi 的技術滿足了關鍵需求:讓資料能以較低功耗更快、更可靠且以更高效能進行傳輸。我們是垂直整合的半導體公司,我們生產的 IP、客製晶片和連接產品由全球一流客戶部署在資料中心、計算、網路、AI、5G、自動駕駛汽車和儲存領域等。公司由一群在半導體 IP 授權擁有良好記錄的專家技術團隊於 2017 年創立,而我們的使命是加速數位世界核心的關鍵資料基礎架構。如欲瞭解有關 Alphawave Semi 的更多資訊,請瀏覽以下網站:awavesemi.com。

Related Chiplet

- Interconnect Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Bridglets

- Automotive AI Accelerator

- Direct Chiplet Interface

Related News

- 小芯片先驱 Eliyan公司加入 UCIe 和 JEDEC 联盟,拓展资深领导团队以加速突破性Die-to-Die互连方案的普及

- OPENEDGES 推出 UCIe 小芯片控制器 IP,扩展产品组合

- GUC 宣布成功推出业界首款采用台积电 3nm 和 CoWoS 技术的 UCIe 32G 芯片

- 领先的半导体厂商、封装商、IP供应商、晶圆代工厂和云服务提供商联合制定小芯片生态系统标准