GUC 宣布 CSP 資料中心採用 HBM3E IP

台灣新竹 – 2024年09月24日 – 先進 ASIC 領導廠商創意電子 (GUC) 很高興宣布,其 3 奈米 HBM3E 控制器和實體層 IP 已獲領先業界的雲端服務供應商 (CSP) 及多家高效運算 (HPC) 解決方案供應商所採用。這款尖端 ASIC 預計將於今年流片,並將採用最新的 9.2Gbps HBM3E 記憶體技術。

創意電子的 HBM3E 控制器和 PHY IP 已被許多 AI 公司採用,創意電子也積極與 HBM 供應商(如美光)合作,為下一代 AI ASIC 開發 HBM4 IP。

創意電子 HBM3E IP 亮點:

- 通過台積電先進製程技術的驗證:台積電 N7/N6、N5/N4P、N3E/N3P 製程。

- 通過所有主流 HBM3 廠商的矽驗證

- 在台積電 CoWoS-S 及 CoWoS-R 技術上均通過矽驗證:創意電子為 TSMC CoWoS-S 設計 eDTC與 CoWoS-R 設計 IPD,以實現最佳電源完整性。

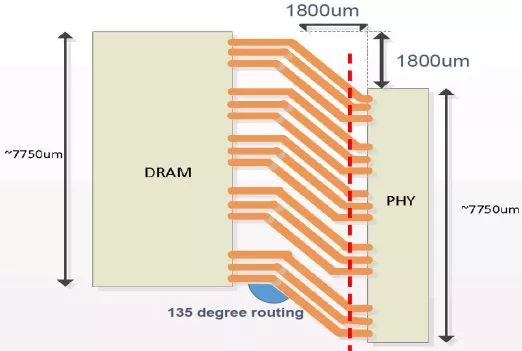

- 高階中介層(Interposer)佈線:專利中介層佈局,既支援具 Y 軸偏移的角度佈線,又能保持最佳的信號完整性及電源完整性。

- 內建小晶片互連監控解決方案:GUC 與 proteanTecs 合作,將小晶片互連監視器整合到 HBM PHY 中。此功能增強了小晶片的可觀察性和可靠性。

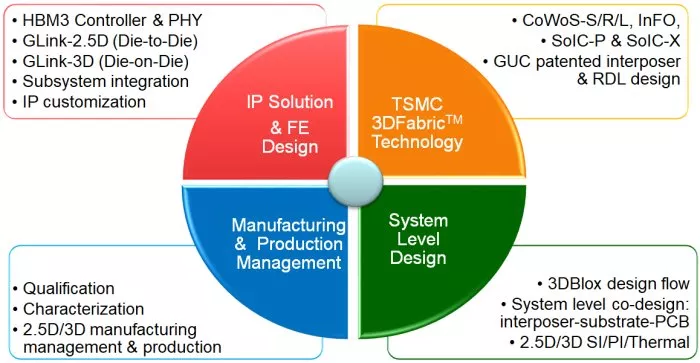

- 完整的2.5/3D多晶片設計服務:創意電子可為 HBM CoWoS ASIC 平台設計提供完整的 2.5D 與 3D 服務的選項。

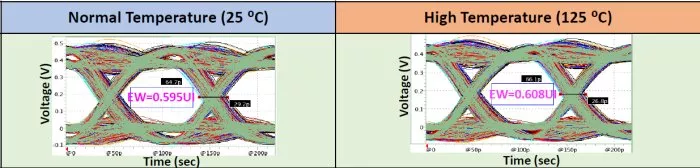

HBM3E 9.2G 眼圖 (Eye Diagram)

中介層 (Interposer) 角度佈線

創意電子提供2.5D/3D ASIC設計全方位服務

創意電子與美光之間的合作證明,創意電子的HBM3E IP 與美光 HBM3E 可以在 CoWoS-S 和 CoWoS-R 技術上實現 9.2Gbps。創意電子測試晶片的矽結果顯示,除了電源完整性 (PI) 與信號完整性 (SI) 結果通過考驗,在不同溫度和電壓角落上也取得優異的眼圖邊限。此外,創意電子的 IP 與美光的 HBM3E 時序參數整合時可展現更有效的匯流排利用率,進一步增強整體系統效能。

「我們很高興看到我們的 HBM3E 控制器和 PHY IP 整合到 CSP 和 HPC ASIC 中。」 創意電子行銷長 Aditya Raina 說。「我們的 HBM3E 解決方案不但經過矽驗證,亦通過多個先進技術與主流廠商的驗證,而持續獲得多家大廠採用,也彰顯出這個解決方案的穩健度與優勢。我們期待繼續為各種應用提供支持,包括人工智慧、高效能運算、網路和汽車。

美光AI Solutions Group的 senior director Girish Cherussery 表示:“記憶體是人工智慧伺服器不可或缺的一部分,也是資料中心系統效能和進步的基礎。”「美光同級最佳的記憶體速度及能源效率表現,非常有益於因應例如 ChatGPT 等大型語言模型這類生成式 AI 工作負載日益增加的需求,進而支援 AI 維持成長步調。」

欲了解更多資訊,請直接聯繫您的創意電子銷售代表,聯絡資訊請參見: https://www.guc-asic.com/en/about-offices.php

Related Chiplet

- Interconnect Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Bridglets

- Automotive AI Accelerator

- Direct Chiplet Interface

Related News

- GUC 业界领先的 TSMC SoIC-X 专用 UCIe Face-up IP 完成投片

- 领先的半导体厂商、封装商、IP供应商、晶圆代工厂和云服务提供商联合制定小芯片生态系统标准

- YorChip, Inc.使用巴塞罗那 RISC-V IP领军企业Semidynamics的IP 方案,推出首款用于边缘 AI 应用的小芯片

- 創意電子為 AI/HPC/網路產業客戶提供完整的3DIC ASIC 套裝服務