Sarcina Technology - Chiplet Ecosystem

Founded in 2011, Sarcina Technology is the Application Specific Advanced Packaging Service that provides a boutique collaborative experience for small-to-mid-sized IC companies. It brings a proven 100% right-the-first time advanced packaging track record of wafer-to-production services that reduce overheads and speeds time-to-volume. For more information, visit sarcinatech.com

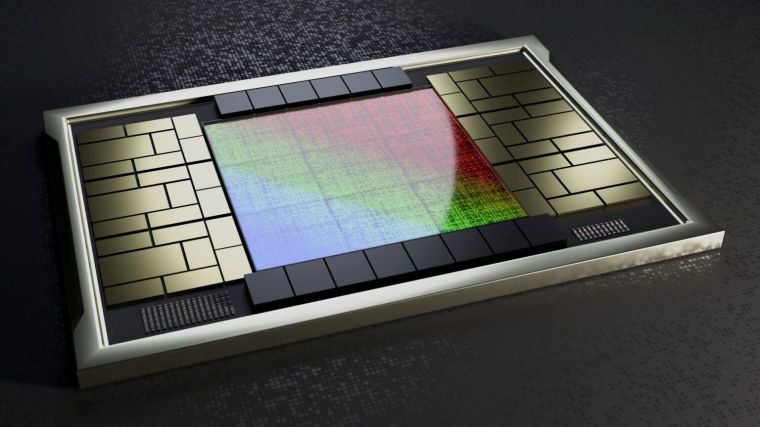

2.5D Silicon Interposer Packaging Technologies

Sarcina designs 2.5D silicon interposer package for artificial intelligence, networking, and other high-performance computing applications. One of its designs in 2018 included an ASIC die and two High Bandwidth Memory (HBM) flip mounted onto a Silicon interposer. The company inserts physical test pattern into every interposer and test them on a 12″ wafer prior to assembly to increase overall yield.

3D Packaging

3D packaging integrates multiple die through traditional interconnection methods such as wire bonding and flip chip to achieve vertical die stacking. Sarcina provides both SiP (System-in-Package) and 3D WLP (Wafer Level Package) in 3D packaging with hybrid bonding pitch as small as 2 µm to reduce package size and minimize manufacturing costs.

Pictured here is a 3D SiP that includes an ASIC die, a LPDDR die, and a Nand Flash die stacked inside a package. The SiP achieved a greater than 98% production yield despite the fact that there are nearly 1000 wires.

Sarcina uses 3D X-ray technology to identify and prevent wire-to-wire short.

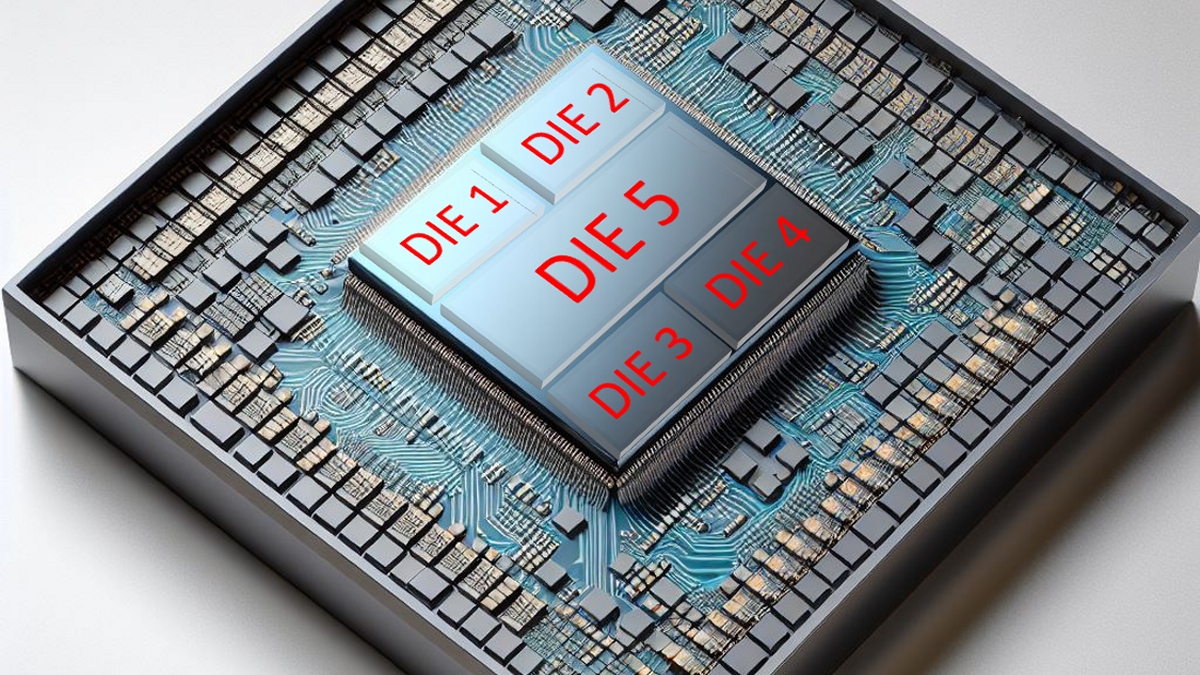

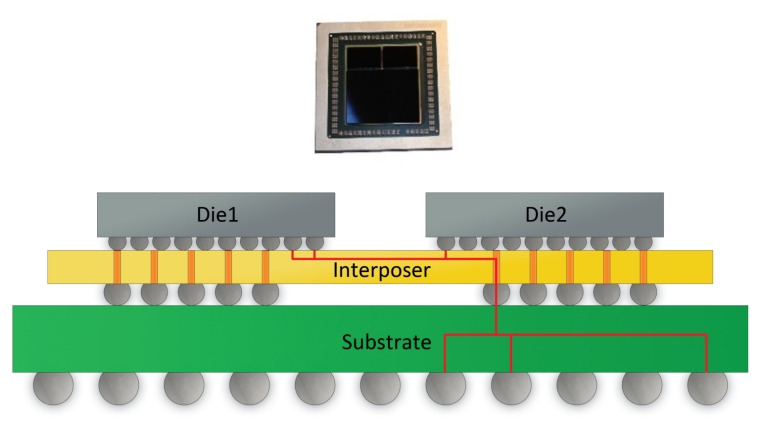

Multi Chip Modules/Chiplet Design

Sarcina has been designing the Multi-Chip Module (MCM) packages for more than a decade. Its packages have been in production for many years.

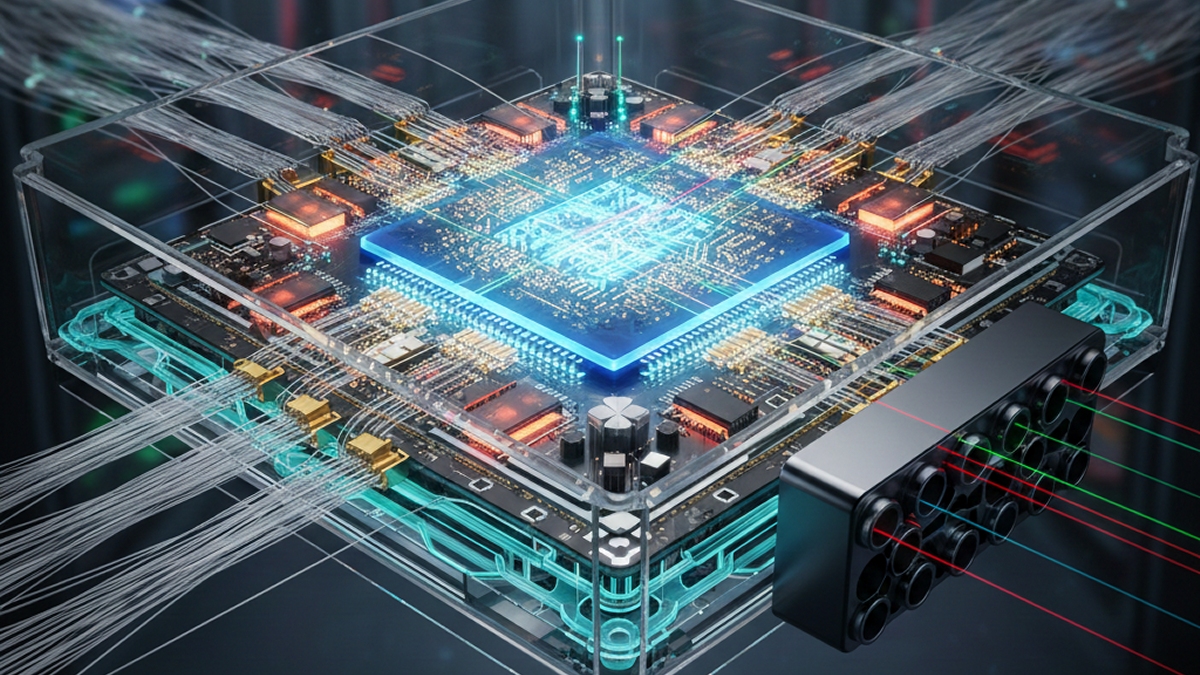

Pictured is a Sarcina package with three chiplets. It has one large ASIC die communicating to the outside world via two nearby I/O dice. Because the new I/O dice offer the next generation SerDes speed, integrating them with the ASIC extended the ASIC chip’s lifetime with little effort and at a fraction of the cost to tape out a new ASIC chip.

The second picture is an illustration of a package with several chiplets flip mounted on a laminate substrate, together with several passive components. A real world example is illustrated in the photonic IC package section.

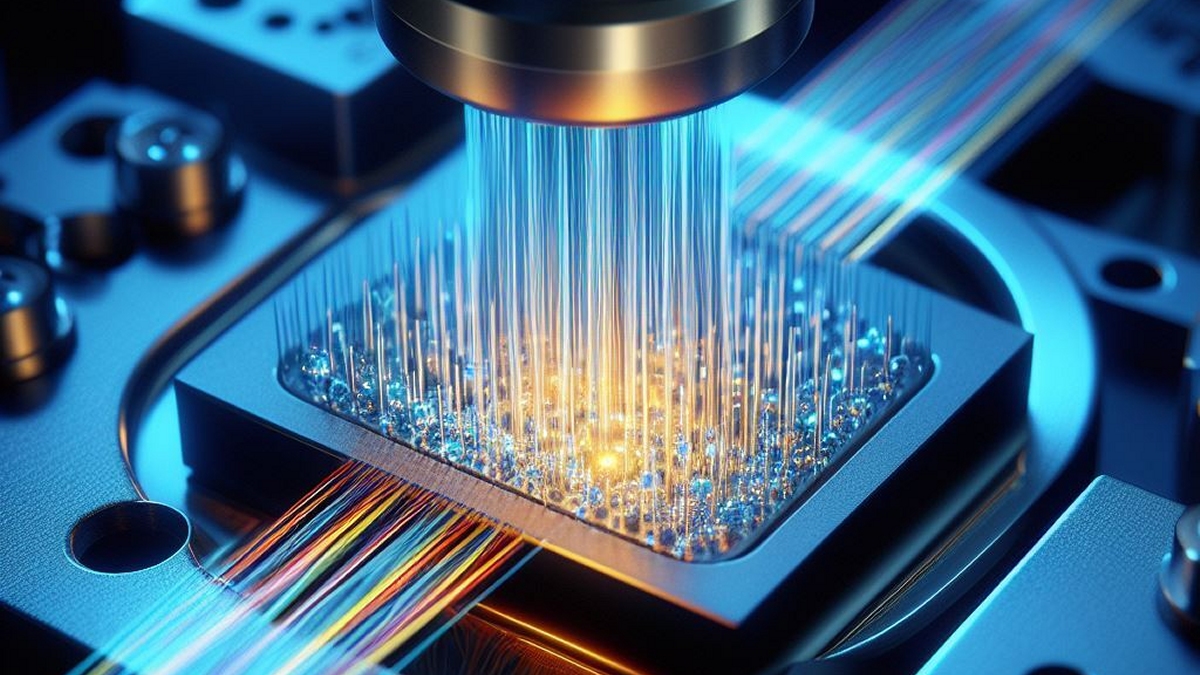

Photonic IC Packaging

Integrating lasers and photo detectors onto an ASIC silicon die to form a photonic IC (PIC) and then to integrate the PIC die with optical fibers in a package provides a more energy efficient way to increase data transmission speed and bandwidth of a digital network. It also reduces electricity costs today and lowers future hardware cost.

In this Sarcina designed package, fibers come in from right side and were coupled to the lasers on the PIC die underneath. This device allows electronic digital signals to be converted to optical signals and then transmitted to optical fibers by integrated lasers inside the PIC die.

Automotive Packaging

Sarcina designs packages for automotive applications to survive stretched temperature ranges, harsh environmental conditions, and pass stringent qualification standards. These designs often require advanced packages with high I/O pin out, high communication speed, high processing performance and high power. Shown in the picture is an artist-rendered GPS chip that accurately determines a vehicle’s position and speed.

What's New

Corporate Headquarters

Sarcina Technology