Optimized Low Parasitic Capacitance ESD Clamps for High-Bandwidth 2.5D/3D Chiplet Interfaces in Advanced FinFET Technology

By Ehsanollah Fallah, Bart Keppens (Sofics)

Abstract

As semiconductor technology advances towards 3nm FinFet, mitigating electrostatic discharge (ESD) risks becomes increasingly vital. Integrating Chiplets introduces reliability concerns, particularly regarding ESD protection for various interfaces. This paper explores ESD mitigation strategies, focusing on internal interfaces crucial for Chiplet applications. Through simulations and measurements, the efficacy of an ESD-on-silicon-controlled rectifier (SCR), as a local clamp approach, is evaluated. Results demonstrate its superiority over conventional methods, offering ultra-low leakage and compact footprint. Furthermore, layout optimization techniques are discussed to minimize parasitic capacitance, essential for high-speed die-to-die interfaces.

Introduction

As Moore’s Law nears its end, scaling transistors for high-performance chips becomes tougher. Expanding chip area is crucial for enhancing performance, but it’s constrained by factors like cost, reticle size and manufacturing yield, leading to the emergence of the “area-wall”[1]. To jump from this wall, the semiconductor industry moved towards embracing Chiplet solutions across various applications. Chiplet solutions offer a promising alternative by exhibiting higher yields for equivalent chip areas, making them advantageous in overcoming the limitations of traditional monolithic chip designs[2]. Additionally, Chiplets enhances flexibility in selecting optimal processes for specific functionalities[3]. Moreover, Chiplet solutions boast reduced footprints while maintaining equivalent functionality compared to monolithic counterparts. Lastly, the reusability of Chiplets as Intellectual Property (IP) blocks promises to decrease overall design costs[4].

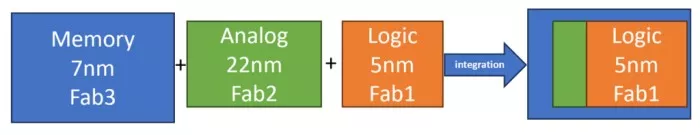

Fig. 1: Representation of the integration of the Chiplet solutions.

Fig. 1 illustrates the integration of a Chiplet solution. Various connectivity standards like UCIe[5], Bunch of Wires (BoW) [6], and Advanced Interface Bus (AIB) [5] have been introduced to facilitate communication between dies. Besides Chiplet advantages, designing a Chiplet-based solution has reliability challenges[7]. One of these challenges is providing effective Electrostatic Discharge (ESD) protection for different interfaces that Chiplets utilize for integration.

In discussions concerning ESD, it is crucial to categorize chip interfaces into two distinct types:

- External Chip Interfaces: These interfaces establish connections beyond the package boundaries, potentially utilizing methods like bond wires or ball/bumps.

- Internal Chip Interfaces: These interfaces are utilized within the package and employ various connection methods as mentioned before.

External interfaces are often integrated into an I/O-ring at the chip’s edge, utilizing various pad types provided by foundries. However, internal interfaces typically don’t require a complete I/O ring, with a small section near the Through-Silicon Via (TSV) sufficing.

On-chip ESD protection devices are crucial for mitigating ESD events on exposed package pins during various phases of the IC product lifecycle, including assembly, transportation, and testing. For the external interfaces, designers should adhere to standard ESD robustness criteria, usually requiring a minimum of 2kV Human Body Model (HBM) and around 300V to 500V Charged Device Model (CDM) protection. However, certain applications like HDMI cables, timing controllers, and SIM card interfaces may demand even higher ESD robustness exceeding 2kV HBM. Conversely, for chip interfaces contained within the package, the ESD robustness requirement can be adjusted. As these connections are sealed within the IC package, the risk of ESD stress during IC transport and PCB assembly is reduced. However, completely eliminating on-chip ESD devices is impractical, as ESD events could still potentially occur during the assembly of different dies inside the package. Nonetheless, such assembly processes are typically carried out under strict ESD-safe conditions, with assembly suppliers providing guidelines for minimum ESD requirements, usually less than 35V CDM[8].

The internal chip interfaces for Chiplet applications often require numerous connections, sometimes reaching several hundred. Each connection necessitates an ESD clamp, highlighting the need to minimize the area occupied by ESD cells. Additionally, many of these internal interfaces operate at high speeds, underscoring the importance of ESD solutions with minimal parasitic capacitance to meet these bandwidth demands effectively. In this paper, our attention is directed solely towards elucidating ESD solutions tailored specifically for Chiplet applications for 3nm and 4nm FinFET, wherein the imperative lies in implementing ultra-small ESD solutions characterized by minimal parasitic capacitance for these kinds of interfaces.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Towards efficient ESD protection strategies for advanced 3D systems-on-chip

- Tiny Chiplets Enabled by Packaging Scaling: Opportunities in ESD Protection and Signal Integrity

- Stop-For-Top IP model to replace One-Stop-Shop by 2025... and support the creation of successful Chiplet business

- Chiplet Strategy is Key to Addressing Compute Density Challenges

Latest Technical Papers

- Link Quality Aware Pathfinding for Chiplet Interconnects

- Effects of Poor Workload Partitioning on System Performance for Chiplet-Based Systems

- Mozart: Modularized and Efficient MoE Training on 3.5D Wafer-Scale Chiplet Architectures

- Network Design for Wafer-Scale Systems with Wafer-on-Wafer Hybrid Bonding

- CarbonPATH: Carbon-aware pathfinding and architecture optimization for chiplet-based AI systems