AuxiliarySRAM: Exploring Elastic On-Chip Memory in 2.5D Chiplet Systems Design

By Zichao Ling, Lin Li, Yi Huang, Yixin Xuan, Jianwang Zhai, Kang Zhao

Beijing University of Posts and Telecommunications, China

Abstract

The “Memory Wall” dilemma remains a critical challenge in modern computing systems. While latency-sensitive applications increasingly rely on costly on-chip SRAM to meet performance requirements, SRAM scaling faces bottleneck. Currently, Chiplet-based techniques present a promising solution to this challenge by enabling optimized trade-offs between latency, capacity, and cost.

The “Memory Wall” dilemma remains a critical challenge in modern computing systems. While latency-sensitive applications increasingly rely on costly on-chip SRAM to meet performance requirements, SRAM scaling faces bottleneck. Currently, Chiplet-based techniques present a promising solution to this challenge by enabling optimized trade-offs between latency, capacity, and cost.

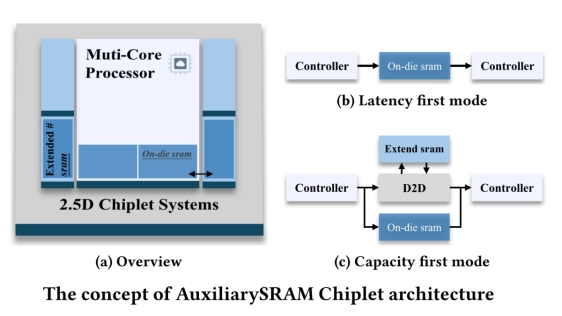

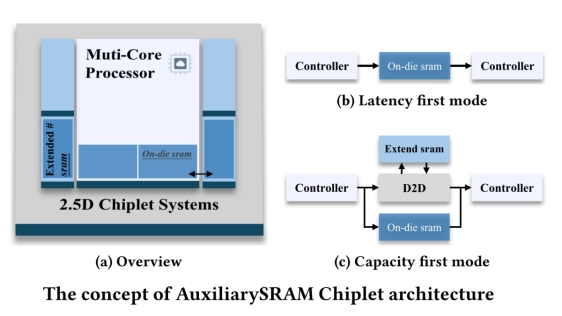

This paper introduces AuxiliarySRAM, a design methodology that decouples SRAM resources into on-die and extended chiplets, enabling elastic capacity-latency scaling. Key contributions include: (1) a lightweight network-on-chip (NoC) with simplified crossbars, dual local ports, and address prediction to reduce average latency by 49.29% and boost bandwidth by 79.35%; (2) a evaluation framework integrated with Bayesian optimization (BO) to resolve Pareto-optimal on/off-die capacity ratios, accelerated by pruning strategies (1.93× speedup); and (3) system-level evaluation provides Pareto frontier-based design guidelines and demonstrates its cost-saving advantages.

Keywords:

Memory Architecture, Chiplet System, Lightweight Network on Chip, Design Space Exploration

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- TDPNavigator-Placer: Thermal- and Wirelength-Aware Chiplet Placement in 2.5D Systems Through Multi-Agent Reinforcement Learning

- Signal Integrity Challenges in Chiplet-Based Designs: Addressing Performance and Security

- Thermal Implications of Non-Uniform Power in BSPDN-Enabled 2.5D/3D Chiplet-based Systems-in-Package using Nanosheet Technology

- Multi-Chiplet Marvels: Exploring Chip-Centric Thermal Analysis

Latest Technical Papers

- Spatiotemporal thermal characterization for 3D stacked chiplet systems based on transient thermal simulation

- Interconnect-Aware Logic Resynthesis for Multi-Die FPGAs

- Scope: A Scalable Merged Pipeline Framework for Multi-Chip-Module NN Accelerators

- Scaling Routers with In-Package Optics and High-Bandwidth Memories

- TDPNavigator-Placer: Thermal- and Wirelength-Aware Chiplet Placement in 2.5D Systems Through Multi-Agent Reinforcement Learning