Redefining SoC Design: The Shift to Secure Chiplet-Based Architectures

The semiconductor industry is undergoing a paradigm shift from monolithic system-on-chip (SoC) architectures to modular, chiplet-based designs. This transformation is driven by escalating design complexity, soaring fabrication costs, and the relentless pursuit of efficiency. However, as chiplet adoption accelerates, security becomes a critical concern, requiring robust measures to protect data, intellectual property (IP), and system integrity.

Industry Trends Driving the Chiplet Transformation

The rapid evolution of semiconductor technology is reshaping SoC development, accelerating the transition to chiplet-based architectures. One of the key drivers of this shift is the ever-increasing compute demands in the physical AI era. As companies race to address those demands, there is an increasing challenge of scaling monolithic SoCs, which are reaching economic and technical limits. Advances in packaging technologies now enable modular chiplets, offering an optimal balance between cost, performance, scalabilty, and manufacturability.

At the same time, industries such as cloud computing, automotive, and AI require highly specialized silicon to optimize efficiency and power management. The shift from standalone IP blocks to integrated chiplet-based system solutions is transforming how semiconductor companies approach design. Additionally, chiplet architectures enable cross-foundry integration, reducing risks associated with single-source manufacturing dependencies and enhancing supply chain resilience. However, this distributed approach also introduces new security challenges, as ensuring trusted execution across multiple chiplets and vendors is more complex than in traditional monolithic SoCs.

The 4 Cs of Chiplet-Based Design

Chiplet architectures address these industry challenges by offering four core benefits. First, they provide cost efficiency by enabling die reuse and optimizing investments in advanced-node manufacturing only where necessary. Second, they allow for customization, with modular architectures that scale across diverse performance requirements. Third, configuration management becomes more streamlined, as chiplet architecture and reuse, generation over generation, simplifies portfolio management, allows for greater levels of integration, and accelerates time to market. Lastly, the richness of the Cadence ecosystem provides for a flexible engagement model from architecture, to IP, to full Arm® CSA (Chiplet System Architecture) and Universal Chiplet Interconnect Express™ (UCIe™)-compliant chips, to fully tested and validated silicon.

Overcoming Security Challenges in Chiplet-Based Architectures

As chiplets become the new standard for SoC design, security is a fundamental enabler rather than an afterthought. Cadence is working with Secure-IC to address these challenges by ensuring secure boot and trust propagation, where chiplets authenticate cryptographically to establish trust within a system-in-package (SiP). This guarantees that only verified components are integrated, mitigating risks from counterfeit or compromised chiplets. Additionally, remote attestation and cryptographic assurance mechanisms, including TPM 2.0, PSA, and DICE frameworks, provide verifiable trust at every level of integration.

One of the most pressing concerns in future-proofing chiplet security is the advent of post-quantum cryptography (PQC). Quantum computing poses a substantial risk to conventional cryptographic algorithms, necessitating the integration of quantum-resistant protocols. Secure-IC’s solutions incorporate PQC readiness, ensuring long-term resilience against emerging threats and protecting sensitive data across connected chiplet-based systems.

Furthermore, compliance with safety and cybersecurity standards is critical, particularly in automotive and industrial applications. Secure-IC’s security solutions align with ISO 26262 (ASIL B and D), ISO/SAE 21434, and UN ECE R.155/R.156 regulations, ensuring that chiplet-based architectures meet the highest levels of functional safety and cybersecurity requirements. These robust security frameworks are crucial as industries transition towards software-defined vehicles and highly autonomous AI-driven systems.

Chiplets Driving Innovation in Automotive and AI

The adoption of chiplet architectures is particularly transformative across the spectrum of physical AI sectors like automotive, robotics, drones, and aerospace and defense systems. In the automotive sector, where semiconductor demand is expected to surpass $300 billion by 2030, chiplets enable scalable architectures for advanced driver assistance systems (ADAS) and autonomous driving, optimizing real-time processing capabilities while maintaining strict security standards. By integrating hardware security modules (HSMs) and secure enclaves directly into chiplets, manufacturers can ensure the protection of sensitive operations, such as over-the-air (OTA) updates and cryptographic key management.

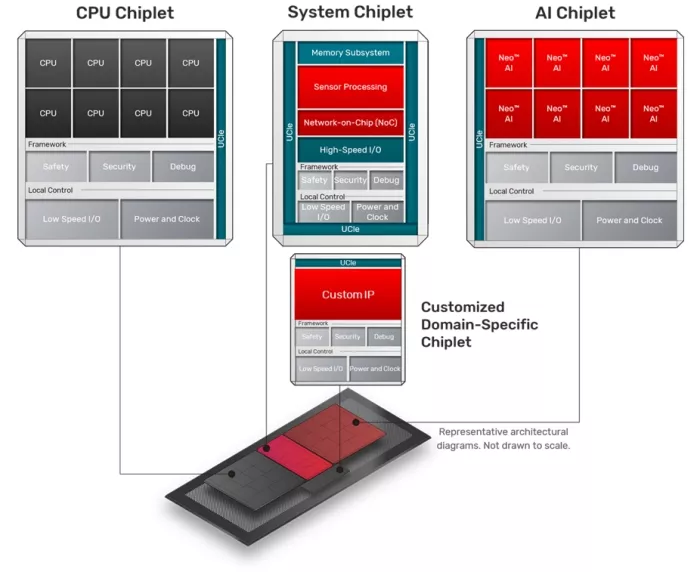

To accelerate time to market, Cadence is offering a chiplet-based physical AI reference platform architecture for multi-chiplet solutions. This platform allows for both the distribution of SoC-level control functionality across multiple chiplets, as well as the local framework for each of the chiplets in the system. The chiplet framework has been defined as having a common language that supports chiplet-to-chiplet communication, interoperability, and behavior. This spec-based framework accelerates design efforts for the construction of interoperable chiplets.

AI applications also benefit from modular AI acceleration, allowing reconfigurable designs that adapt to evolving workload demands. Secure-IC’s security-by-design approach ensures that AI chiplets can implement trusted computing functions while safeguarding proprietary machine learning models against IP theft or tampering. By fine-tuning silicon customization, chiplets help balance performance with energy efficiency, a crucial factor for next-generation computing systems. However, this balance must also extend to cybersecurity, where energy-efficient cryptographic engines and real-time threat detection mechanisms protect against attacks without compromising power budgets.

Cadence's Arm-Based System Chiplet and Secure-IC’s Role in Its Security

A landmark development in the chiplet landscape comes from November’s announcement of Cadence’s first Arm-based system chiplet, marking a pivotal step in advancing chiplet technology. This chiplet integrates processors, system IP, and memory IP within a single package, interconnected through the UCIe standard interface. This system chiplet, developed in collaboration with Arm, adheres to Arm's CSA standard, which ensures interoperability and accelerates time to market for chiplet-based solutions.

In this groundbreaking achievement, Secure-IC played a crucial role in ensuring the integrated security. Secure-IC's expertise was vital in implementing zero-trust provisioning, secure boot, cryptographic trust, and the necessary protection mechanisms to ensure the chiplet’s integrity. By embedding Secure-IC’s security solutions into the tapeout of Cadence's Arm-based system chiplet, it has fortified this pioneering technology, ensuring robust data protection and system reliability in environments requiring high performance and trust. The Cadence Based System Chiplet was given the Embedded World 2025 Award, in the Hardware Category.

Conclusion

Chiplet-based architectures mark a transformative shift in SoC design, delivering breakthrough efficiencies, scalability, configurability, and security. With the offering of Cadence’s chiplet physica AI reference platform and dedicated chiplet frameworks, Cadence is helping customers accelerate time to market and cost efficiencies for their next-generation designs.

With multiple chiplets integrated from various vendors, ensuring secure communication, trusted execution, and protection against potential threats becomes more complex. Security needs to be a cornerstone of chiplet-based designs, ensuring data integrity, preventing counterfeiting, and enabling future-proof resilience through mechanisms like PQC. Cadence and Secure-IC are at the forefront of addressing these concerns, embedding robust security into every layer of the chiplet ecosystem.

From IP to wafers and everything in between, Cadence is helping customers win with the Arm chiplet ecosystem, addressing the ever-increased compute demands in the physical AI era. Stay ahead in semiconductor innovation—explore the future of SoC design with Cadence and Secure-IC!

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Blogs

- Embracing the Chiplet Journey: The Shift to Chiplet-Based Architectures

- Cadence Collaborates with TSMC to Shape the Future of 3D-IC

- Arm Zena CSS – Accelerating Chiplet-Based SoC Design for AI-Defined Vehicles

- From Blocks to Systems: Understanding Chiplets in SoC Design

Latest Blogs

- Advancing High‑Performance Silicon Photonics and Silicon Germanium (SiGe) for the Next Era of Optical Connectivity

- Accelerating Chiplet Innovation with a New Partner Ecosystem

- Accelerating Multi-Die Innovation: How Synopsys and Samsung are Shaping Chip Design

- Six critical trends reshaping 3D IC design in 2026 and beyond

- AI Energy Gap and Chiplets: Why Data Movement Matters