An Open Framework for exploring Architecture Interoperability driving multi-vendor Chiplet Eco-systems

This post builds on Part 1 of our blog series Accelerating early-stage architecture explorations which outlined the motivation and benefits of establishing an open framework for multi-vendor virtual prototyping. In this installment we present a draft proposal to initiate industry-wide dialog and collaboration.

The objective is to define a widely accepted open framework for virtual prototyping of Systems in Package (SIPs) composed of replicated dies and chiplets.

Proposed Framework in more detail

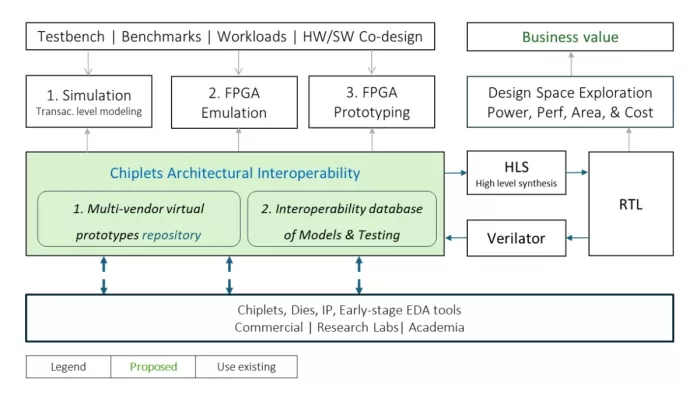

The proposed framework builds on foundation of commercial & open-source tools with 5 key deliverables (refer to figure below):

- Multi-vendor model repository: A centralized platform to host system-level models from various organizations.

- Curated stimuli suite: Test benches, benchmarks, and workloads for validating the models.

- Interoperability verification methodologies: Simulation, emulation, and FPGA based prototyping using available tools in commercial, research labs, and academia.

- Interoperability Database: A structured listing of models and their architectural interoperability levels with other select models

- Process flows and Governance: Minimal standards for testing, version control, and collaborative development.

Elaborating above in some more detail:

Repository

- A collaboration platform for storing, updating, and tracking system-level models. Behavioral or functional models are at a higher level of abstraction compared to RTL models.

- Ability to store SystemC or similar models. SystemC has been an IEEE standard for many years. We expect large pool of SystemC models developed over the years some of which could seed the repository https://systemc.org/overview/systemc/

- Facilitates recommendation of model matches based on desired function and criteria, using automation.

- Other features include private repositories, role-based access control, and forking restrictions.

- Automation of process flows including testing and deployment.

- Links to popular commercial/research tools used for chiplet prototyping.

Curated Stimuli suite

Recommended suite of test benches, benchmarks, workloads, and software for HW/SW co-design. A minimum curated set will be decided during the framework definition process. Higher levels of interoperability verification drive higher levels of confidence in the models.

Interoperability Verification Methodologies:

Three levels of architectural interoperability verification that tradeoff stimuli intensity, cost, and time.

- Simulation

- ~50× faster than RTL simulation

- Medium confidence level

- Runs test benches and partial benchmarks

- Options for timed or loosely timed simulation

- Emulation

- Event-driven, emulation on FPGA

- Suitable for more intensive benchmarks

- Prototyping on FPGAs

- Higher confidence and speed

- Demonstrates comprehensive benchmark suites and workloads

- Enables HW/SW co-design

Verilator

Verilator is a widely adopted open-source tool that compiles RTL code to SystemC/C++ models. It has a long and proven history and is used in many organizations https://github.com/verilator/verilator.

For organizations with existing RTL code, Verilator allows compilation to SystemC modules. The compiled model is about 100x-faster than interpreted Verilog simulators. Behavioral model abstracts away intellectual property (IP) in RTL code and is a great starting point for compatibility testing. These models can be populated into the repository for interoperability verification with other models.

Enables sharing of abstracted models while protecting the IP in RTL code. Enables market research, i.e., testing level of interest in the industry for specific system models.

High level synthesis, HLS

One process flow allows synthesis of high level system models to RTL code. This facilitates higher confidence estimation of performance, power, and area supporting rapid design space exploration. HLS reduces manual RTL coding for faster, broader, and scalable estimations across multiple design configurations.

Design Space Exploration and Business Value

One of the key features of an open framework is enabling design space exploration with abstracted models from multiple organizations. Models of reference designs and verification IP may also be used to test architectural interoperability.

Minimum proof points combine viable design elements with appropriate stimuli to prove technical value of performance, power, and area. When linked to well-established die cost models this allows estimate of costs and business case estimation.

For SiPs based on multiple dies and chiplets business value is typically derived from:

- Outsourcing non-core chiplet functionality

- Feature enhancement via third-party chiplets

- Reusing select dies/chiplets across design portfolio

- Reusing select dies/chiplets on older process nodes

- Board to package level aggregation

- Innovative or specialized chiplets

Exit to Implementation phase

Once promising architectural interoperable matches are identified, organizations may advance to the design and implementation phase, leveraging their choice of tools and methodologies best suited for their workflows.

In summary, by defining an open framework the industry accelerates a collaborative approach to speedy discovery and evaluation of dies, chiplets, and IPs. This enables better product-market fit, higher ASP, faster time-to-market, leverage IP, lower cost, lower NRE, and business case for investment decisions.

Resources and Call-to-action:

- Visit Call for Participation: https://www.opencompute.org/events/upcoming-events/cfp-open-framework-for-chiplet-eco-system-virtual-prototyping

- Open systems for AI workshop: https://www.opencompute.org/events/past-events/ocp-aiml-it-infrastructure-silicon-workshop

- Deck: https://drive.google.com/file/d/1lsUX4Autk-Xt35zycQ1250fMhkJapbfX/view?usp=drive_link

- Video Virtual chiplet prototyping starts at min 34:00: https://www.youtube.com/watch?v=Pg82RjT84nU

- Attend OCP Global Summit session “Accelerating Early-Stage Exploration with Virtual Prototyping for a Flourishing Multi-Vendor Chiplet Economy” , Wed, October 15, 2025 in San Jose, CA https://2025ocpglobal.fnvirtual.app/a/schedule/

Related Chiplet

- Interconnect Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Bridglets

- Automotive AI Accelerator

- Direct Chiplet Interface

Related Blogs

- Accelerating an Open Chiplet Ecosystem for Automotive with Foundation Chiplet System Architecture

- Accelerating Early-Stage explorations with Virtual Prototyping for a thriving multi-vendor chiplet ecosystem

- Call for Participation (CFP) Open Framework for Chiplet Eco-system Virtual Prototyping

- AMI Outlines Full Support for Arm Total Design Chiplet Architecture to Custom Silicon Designers and Producers at APAC ATD Summit

Latest Blogs

- 3D-IC Market Outlook: Technology Roadmaps, Readiness, and Design Implications

- Cadence 3D-IC Success Stories: Faster Bandwidth, Lower Power, On-Time Tapeouts

- 3D-IC Test and Reliability: KGD Strategies, Access Architecture, & Failure Mode

- 3D-IC in AI, HPC, and 5G: Bandwidth, Latency, and Energy per Bit Advantages

- Bosch and the chiplet revolution: Enabling software-defined mobility