ATSim: A Fast and Accurate Simulation Framework for 2.5D/3D Chiplet Thermal Design Optimization

By Qipan Wang 1,2, Tianxiang Zhu 1, Jiajia Cui 1, Yicheng Wei 1, Linxiao Shen 1, Zhe Cheng 1, Runsheng Wang 1,3,4, Ru Huang 1,3,4, Yibo Lin 1,3,4

1 School of Integrated Circuits, Peking University

2 Academy for Advanced Interdisciplinary Studies, Peking University

3 Institute of Electronic Design Automation, Peking University, Wuxi, China

4 Beijing Advanced Innovation Center for Integrated Circuits, Beijing, China

Abstract

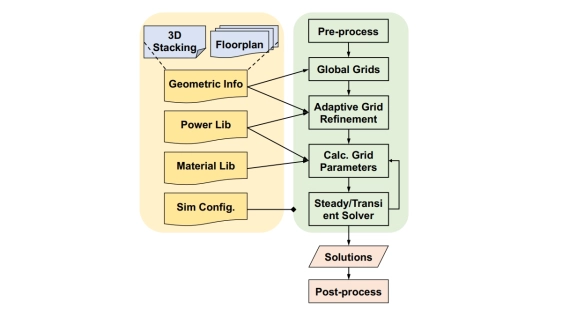

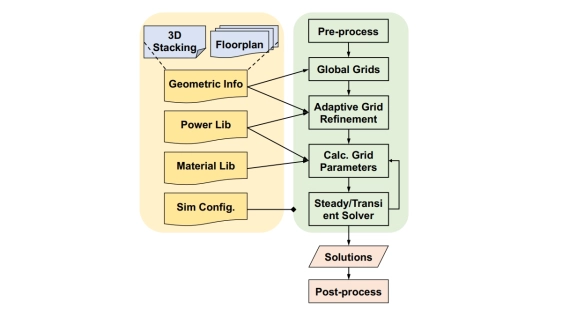

This paper reviews the thermal challenges in 2.5D/3D chiplet integration systems and introduces ATSim, a simulation framework with applications to chiplet thermal optimization. ATSim enables fast and accurate thermal simulation for both steady-state and transient conditions. It supports nonlinear, heterogeneous, and anisotropic materials. The framework features a multilevel grid generation scheme based on a novel hybrid tree structure. Compared to mainstream academic and commercial tools, ATSim achieves high accuracy and efficiency, making it a powerful tool for evaluating and improving thermal designs, including applications like thermal-aware placement.

This paper reviews the thermal challenges in 2.5D/3D chiplet integration systems and introduces ATSim, a simulation framework with applications to chiplet thermal optimization. ATSim enables fast and accurate thermal simulation for both steady-state and transient conditions. It supports nonlinear, heterogeneous, and anisotropic materials. The framework features a multilevel grid generation scheme based on a novel hybrid tree structure. Compared to mainstream academic and commercial tools, ATSim achieves high accuracy and efficiency, making it a powerful tool for evaluating and improving thermal designs, including applications like thermal-aware placement.

To read the full article, click here

Related Chiplet

- Interconnect Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Bridglets

- Automotive AI Accelerator

- Direct Chiplet Interface

Related Technical Papers

- DeepOHeat-v1: Efficient Operator Learning for Fast and Trustworthy Thermal Simulation and Optimization in 3D-IC Design

- 3D-ICE 4.0: Accurate and efficient thermal modeling for 2.5D/3D heterogeneous chiplet systems

- Fast and Accurate Jitter Modeling for Statistical BER Analysis for Chiplet Interconnect and Beyond

- Muchisim: A Simulation Framework for Design Exploration of Multi-Chip Manycore Systems

Latest Technical Papers

- Thermo-mechanical co-design of 2.5D flip-chip packages with silicon and glass interposers via finite element analysis and machine learning

- High-Efficient and Fast-Response Thermal Management by Heterogeneous Integration of Diamond on Interposer-Based 2.5D Chiplets

- HexaMesh: Scaling to Hundreds of Chiplets with an Optimized Chiplet Arrangement

- A physics-constrained and data-driven approach for thermal field inversion in chiplet-based packaging

- Probing the Nanoscale Onset of Plasticity in Electroplated Copper for Hybrid Bonding Structures via Multimodal Atomic Force Microscopy