Defect Analysis and Built-In-Self-Test for Chiplet Interconnects in Fan-out Wafer-Level Packaging

By Partho Bhoumik, Christopher Bailey, and Krishnendu Chakrabarty

School of Electrical, Computer and Energy Engineering, Arizona State University

ASU Center for Semiconductor Microelectronics (ACME), Arizona State University

Abstract

Fan-out wafer-level packaging (FOWLP) addresses the demand for higher interconnect densities by offering reduced form factor, improved signal integrity, and enhanced performance. However, FOWLP faces manufacturing challenges such as coefficient of thermal expansion (CTE) mismatch, warpage, die shift, and post-molding protrusion, causing misalignment and bonding issues during redistribution layer (RDL) buildup. Moreover, the organic nature of the package exposes it to severe thermo-mechanical stresses during fabrication and operation. In order to address these challenges, we propose a comprehensive defect analysis and testing framework for FOWLP interconnects. We use Ansys Q3D to map defects to equivalent electrical circuit models and perform fault simulations to investigate the impacts of these defects on chiplet functionality. Additionally, we present a built-in self-test (BIST) architecture to detect stuck-at and bridging faults while accurately diagnosing the fault type and location. Our simulation results demonstrate the efficacy of the proposed BIST solution and provide critical insights for optimizing design decisions in packages, balancing fault detection and diagnosis with the cost of testability insertion.

I. Introduction

Advanced packaging has emerged as a pivotal solution for extending the capabilities of integrated circuits (ICs) [1]. Traditionally, semiconductor devices were designed as large monolithic dies, but as circuits became more complex, industry shifted toward dividing these large dies into smaller, specialized chiplets with higher yields. These chiplets can be interconnected to enable heterogeneous integration, facilitating the development of advanced 2.5D and 3D packages [2, 3].

Among the various advanced packaging techniques, fan-out wafer-level packaging (FOWLP) offers several advantages over conventional methods, including enhanced electrical performance, reduced form factor, and higher I/O density [4, 5, 6]. This approach involves using a secondary wafer to position the dies with more separation, thereby allowing the extra area to develop redistribution layers (RDL) that connect the neighboring dies via Cu pillars grown on the die pads. However, coefficient of thermal expansion (CTE) mismatch, warpage, and misalignment during bonding can lead to defects that compromise the integrity of the interconnects [7, 8, 9, 10, 11, 12]. A comprehensive study of these defects is essential to understand the impact of defect size and develop test solutions.

Our goal is to tackle the problem of modeling and assessing the impact of various defects within Cu pillars and RDL in a FOWLP package. These defects can originate both during packaging unit processes (such as the RDL build-up processes) and in-service operations due to thermo-mechanical loads [13, 14]. Our approach leverages finite element analysis (FEA) to extract the parasitics corresponding to various defect levels, utilizing the Ansys Q3D tool. We show how the impact of these defects can be analyzed by mapping them to their equivalent faulty circuits.

Furthermore, built-in self-test (BIST) solutions are essential for advanced packaging [15]. BIST can be used to detect and locate opens and shorts within interconnects. Once faults are detected and localized, rerouting strategies can be employed to repair the faulty connections. Despite its importance, there has been limited research on package-level BIST. In [16], a physically aware test method was proposed for interconnects. This method utilizes an array of pattern generators to apply patterns through the chiplet I/Os. However, it does not define fault models or specify test patterns for these models. It also lacks a fault detection mechanism and a diagnostic scheme for failure analysis. The authors in [17, 18] investigated test pattern generation schemes and proposed a test method using automated test equipment and die-wrapper registers to apply the patterns. A total of 16 patterns (4 unique codewords) can test for hard and weak defects within chiplet interconnects. However, scanning test patterns in and out of the tester for thousands of I/Os takes a prohibitive amount of time. An on-chip solution that addresses both post-assembly and in-field fault scenarios is essential for lifecycle monitoring.

In this paper, we tackle the challenges associated with detecting and localizing defects within chiplet interconnects. We begin by analyzing these defects, which allows us to identify and quantify their physical and electrical characteristics. This detailed analysis also helps us to understand the relationship between defects and fault models. Based on these fault models, we propose an efficient approach involving only three test patterns to detect, diagnose and localize all interconnect stuck-at-faults (SAFs) and bridging faults. The main contributions of this paper are listed as follows:

- We provide a comprehensive characterization of defects inside Cu pillars and RDL.

- We demonstrate how to map defects in package components to their equivalent faulty circuits and perform package-level fault simulation using HSPICE.

- We present a BIST architecture that detects, locates, and diagnoses stuck-at (SA) and bridging faults. The BIST outcomes can be combined with defect simulation results to identify the extent of deformities in Cu pillars and RDLs.

The rest of the paper is organized as follows. Section II provides background on FOWLP and FEA. Section III describes the proposed defect analysis framework and equivalent faulty circuits. In Section IV, the BIST architecture is presented and evaluated, and BIST outcomes are mapped to deformities in package components. Section V concludes the paper.

II. Background

II-A. Fan-out Wafer Level Packaging

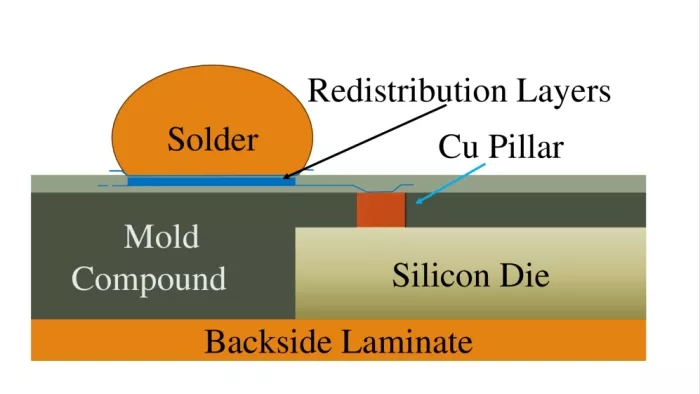

Conventional packaging technologies, such as flip-chip, FOVEROS, EMIB, and CoWoS, rely heavily on substrates or interposers [19], which introduce additional layers, cost, and complexity. FOWLP is an alternative approach that encapsulates the entire die within a molding compound, creating a smooth and continuous surface. In a chip-first, face-up FOWLP method, Cu pillars are first grown at the I/O locations on the native semiconductor wafer. After that, the dies are placed on a reconstituted wafer panel using the die pick and place method. During panelization, the dies are covered on both the front and sides with epoxy molding compound (EMC), with the Cu pillars providing the current pathways through the mold. The panel is then processed by building up interconnections between the exposed Cu pillars and the Cu RDL. An epoxy laminate is applied to the backside of the panel to fully encase the die in epoxy; see Fig. 1. Adaptive Patterning (AP) is used to dynamically scan the position of the Cu bumps and adjust interconnect routing to reduce the impact of die shift [20].

Figure 1: Illustration of a fully molded FOWLP structure [21].

Testability solutions for this promising technology have yet to be studied. [21] demonstrated a test vehicle approach to assess interconnect continuity using a daisy chain. This approach is limited to test vehicles and does not extend to practical applications. Ansys modeling was carried out to simulate the thermal cycling performance of the test package, focusing on strain energy density distribution in critical solder joints. However, there are many other sources of defects that need to be studied. Comprehensive design for test structures is necessary to detect, diagnose, and repair defects.

II-B. Finite Element Analysis

FEA begins by creating a mesh of the object, applying appropriate boundary conditions and loads, and solving mathematical equations describing each element’s physical behavior. While traditional FEA is used for mechanical and thermal analysis, tools such as Ansys Q3D extend these principles to the electromagnetic domain, enabling precise extraction of electrical parasitics. Ansys Q3D Extractor is a 3D quasi-static electromagnetic field simulator that directly extracts parasitic parameters (R, L, C) for complex 3D structures.

III. Defect Analysis

III-A. Defects and Equivalent Circuits

Cu Pillars: These vertical elements extend from the Si die through the molding compound and connect to the RDL. The CTE mismatch between copper (CTE six times higher than silicon [22]) and the other materials can induce significant thermal and mechanical stress. This stress may result in cracks or fractures within the Cu pillars. Moreover, adaptive patterning utilized in FOWLP is highly sensitive, and minor deviations during dynamic scanning can lead to increased contact resistance between Cu bumps and RDL [20]. Furthermore, improper warpage management can cause small-pitch Cu pillars (20 µm) to be shorted to each other.

RDL: The RDL pitch can be as small as 2 µm. At such fine pitch, residue and dust particles can lead to bridging and increased coupling between adjacent lines [23]. Additionally, incomplete or over-etching during manufacturing can damage RDL layers. The above defects are summarized in Table I.

TABLE I: Summary of defects and root causes.

| Component | Defect Type | Root Cause |

|---|---|---|

| Cu Pillars | Cracks/Breaks | CTE mismatch |

| Misalignment | AP deviation or Cu smearing | |

| Bridge | Warpage-induced merging | |

| RDL | Coupling | Dielectric-conductor proximity |

| Bridge | Metal residue during fabrication | |

| Damaged RDL | Etching errors, electromigration |

III-B. Fault-free RLC Extraction and Equivalent Circuit

Before modeling defects, it is essential to first determine the RLC parameters of the interconnect components in the nominal case. We created the geometry of these three elements using Q3D Extractor. The dimensions and material of the elements, along with the extracted parasitics, are presented in Table II. Note that the RDL length will vary depending on the placement of chiplets. To account for this variability, we provide an equation derived from our simulation to calculate the self and mutual capacitance of RDL for any length L.

TABLE II: Details about the interconnect components.

| Property | Cu Pillar | RDL |

|---|---|---|

| Dimensions | d: 20 µm h: 20 µm |

L µm × 2 µm × 2 µm |

| Resistance | 1.11 mΩ | 4.31 mΩ/µm |

| Self Capacitance | 3.21 fF | (1+(L/5−1)×0.72)×0.7 fF |

| Mutual Capacitance | Negligible | 0.092×L fF |

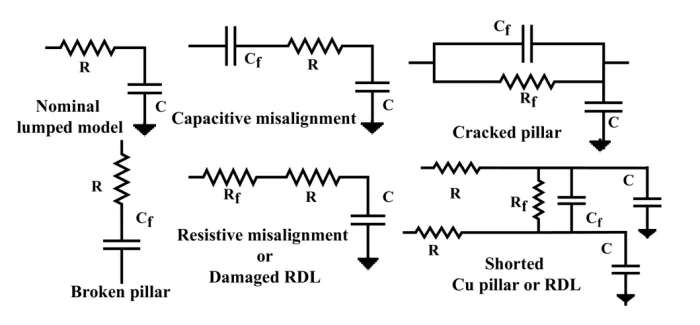

The resistance values for all components closely align with the hand-calculated results, whereas the capacitance values are higher than expected. The discrepancy arises because the simplification for hand calculation does not account for fringe effects at the edges of the device. In reality, fringe effects can contribute up to 50% of the total capacitance at this dimension [24], resulting in higher overall values than calculated. Nevertheless, we can conclude that Q3D accurately models these effects, offering realistic and comprehensive capacitance parasitics. The lumped simulation model of a Cu pillar and RDL segment is illustrated in Fig. 2.

III-C. Ansys Modeling and Equivalent Faulty Circuits

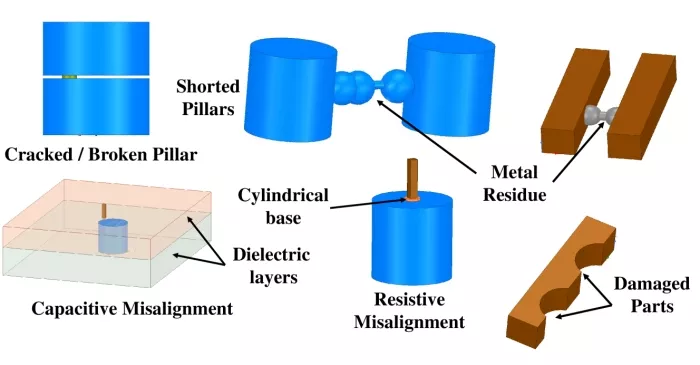

Cu Pillars: We consider a crack at a height of 10 µm within the Cu pillar, characterized by a thickness of 0.5 nm. This defect is introduced in such a manner that it does not extend across the entire cross-sectional area of the pillar, thereby preserving a residual conductive path, as depicted in Fig. 3. Based on the remaining conductive cross-section, we extract the resistance Rf and capacitance Cf values to develop the equivalent faulty circuit associated with this defect (Fig. 2). In cases where the pillar is completely severed with no conductive path remaining, a capacitance is formed between the top and bottom segments of the pillar. For this scenario, only the Cf value needs to be considered.

Figure 2: Equivalent nominal and faulty circuits for Cu pillars and RDL.

Misalignment with the RDL can manifest in two ways:

- Resistive Misalignment: This defect occurs when the RDL maintains contact with the pillar, but the overlap between the two components decreases due to die shift. The reduction in surface contact area increases resistance, which we model as Rf. We add a cylindrical base atop the pillar to serve as the RDL contact point. By varying the area of this cylindrical base, we extract the misalignment-induced resistance for various defect severities. Note that incomplete bonding due to pressure and thermal effects may introduce additional contact resistance, which must be incorporated into the extracted value as the Q3D tool does not account for these extrinsic factors.

- Capacitive Misalignment: This occurs when the RDL fails to make proper contact with the Cu bump (Fig. 3), leaving a gap that forms a capacitive defect modeled by Cf in Fig. 2.

To simulate bridging defects, we introduce metal residues modeled as a combination of spherical and cylindrical geometries that span between adjacent bumps (Fig. 3). The radius of this conductive bridge is varied to account for different levels of defect severity, with Q3D being used to extract the corresponding resistance Rf.

Figure 3: Ansys modeling of Cu pillars and RDL.

RDL: The analysis of RDL bridging defects mirrors that of the Cu pillar. However, the finer pitch (2 µm) of the RDL results in a shorter short-circuit path, thereby amplifying the impact of the defect when compared to Cu bumps. Additionally, the coupling capacitance between adjacent RDL layers, which is neglected for Cu bumps due to their larger pitch (20 µm), must be considered here. The metal residue between two adjacent RDL layers is shown in Fig. 3. Two 10 µm RDL sections are considered to compute the Rf for the short.

(a)

(b)

(c)

(d)

(e)

(f)

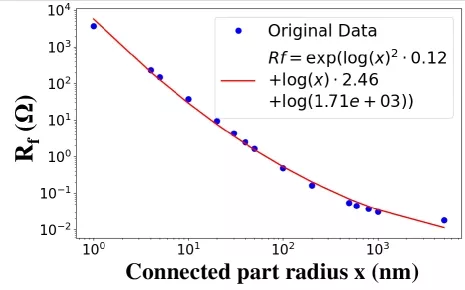

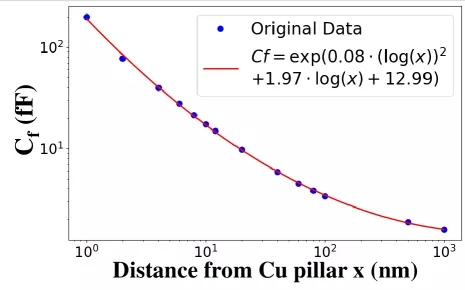

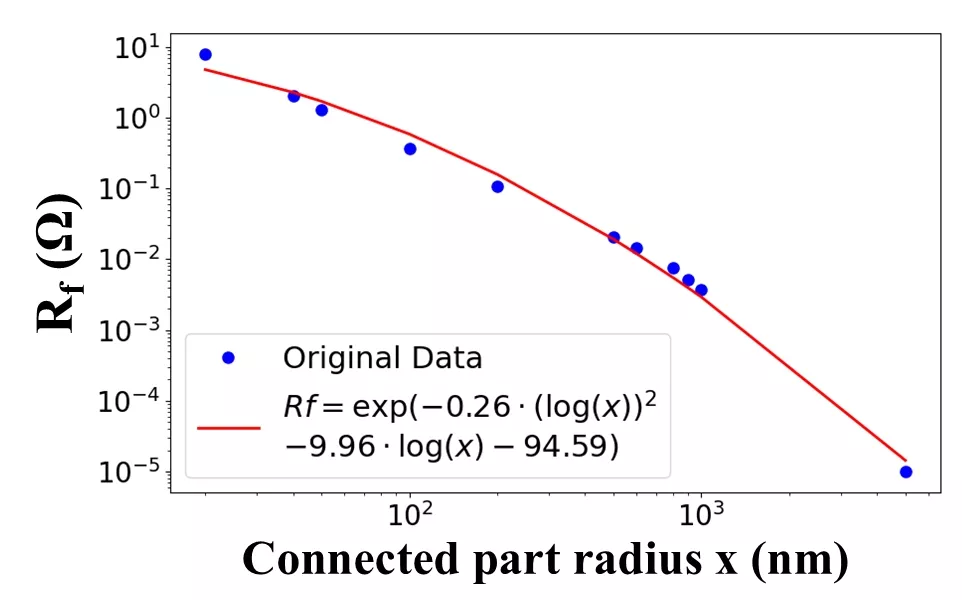

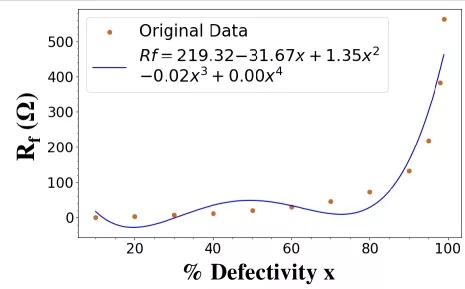

Figure 4: Extracted parasitics for defects in: (a) cracked pillars; (b) shorted pillars; (c) capacitive misalignment; (d) resistive misalignment; (e) damaged RDL; (f) shorted RDL.

To analyze defects within RDL, we created a geometry of a 10 µm section. We considered two points in this section that can be etched out in the worst-case scenario. We assume that this defect is continuous for a RDL of longer length (e.g., 100–200 µm). It is modeled by adding a resistor Rf to the RDL equivalent circuit (Fig 2). The extracted values correlate with the percentage of defective cross-sections of this element.

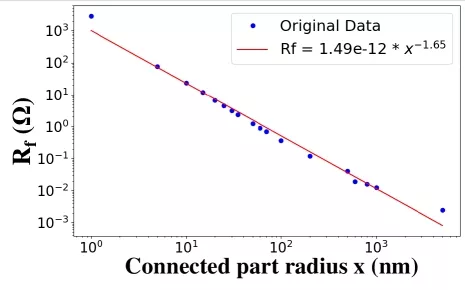

III-D. Simulation Results

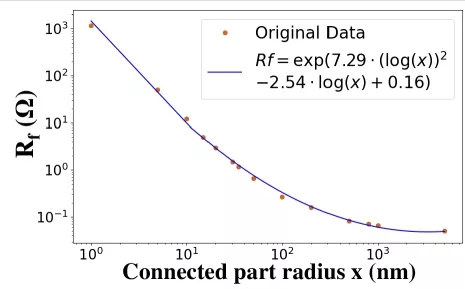

The simulation results are summarized in Fig. 4. For each scenario, we use Python’s log-linear, polynomial, or exponential curve fitting functions and generate equations that accurately model the extracted RC data. These equations are valuable for interpolating or extrapolating defect sizes.

Recall that the elements were not completely disconnected in the case of the Cu pillar cracks; therefore, the model can only define one conductor or net. Under this condition, a capacitance solver find the capacitance Cf . However, since the cross-sectional area of the conductive path is small compared to the total cross-section of these elements, we extract Cf from the fully broken or fractured conditions of these elements. These values can then be incorporated in the equivalent faulty circuit for the cracked case. The extracted Rf values for a cracked Cu pillar are shown in Fig. 4(a).

The fitted model for bridging defects in the Cu pillar exhibits a steeper trend than that of the RDL, as demonstrated in Fig. 4(b) and Fig. 4(f). This difference arises because the pitch of the RDL is ten times smaller than that of the Cu bumps. Therefore, when a bridging defect occurs in RDL, the impact of the defect is much more critical for signal integrity.

Fig. 4(c) and Fig. 4(d) illustrate the RC parasitics for misaligned bonding of Cu pillar and RDL. An exponential relationship between the defect size and the degree of misalignment is evident, highlighting the importance of precise patterning. Fig. 4(e) presents the extracted Rf values for the defective RDL. It is important to note that these values are based on a 10 µm section of the RDL, and appropriate extrapolation is needed for other lengths.

III-E. Fault Analysis

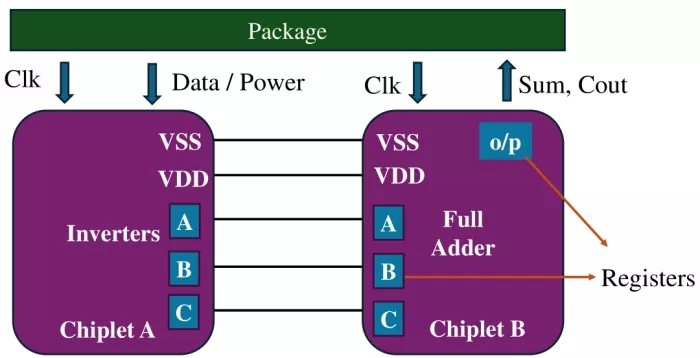

To analyze the functional impact of defects, we perform package-level simulations in HSPICE using OPENROAD ASAP7 PDK, as shown in Fig. 5. In this setup, Chiplet A is modeled with inverters for processing signals from the package; Chiplet B contains a full-adder circuit. All I/Os are wrapped with registers to emulate a real-world core. Using equivalent faulty circuits, we identify defect size thresholds that lead to catastrophic functional failures. These defect sizes are then mapped to the extent of structural deformities using the results presented in Section III-D.

Figure 5: HSPICE setup for package-level fault simulation.

For example, capacitive misalignment or a deformation (break) in Cu bump introduces an open defect (Copen). Such an open in VDD (VSS ) results in a SA-0 (SA-1) fault at chiplet B. An open in VDD creates a floating node and the registers in chiplet B interpret this floating value as logic 0. Conversely, for VSS, the logic circuits at chiplet B establish a connection between VDD and VSS, raising the VSS potential to VDD, thereby causing a SA-1 fault. Interference from the signal lines on VDD and VSS was noticeable in the presence of open defects, but it did not cause any functional failures in the simulation. However, when an open defect occurs in signal wires (e.g., wire A), coupling effects are more prominent. For instance, if A and B are capacitively coupled, B significantly interferes with A. Beyond a critical misalignment gap (≈ 20 nm), net A follows B entirely, and this behavior can be modeled as either a wired-AND (w-A) or wired-OR (w-O) fault. The threshold value of (Copen) increases with coupling effects, meaning that even smaller opens can trigger catastrophic faults as coupling increases.

TABLE III: Functional faults associated with defect size.

| Defect Type | Defect Size | Functional Fault |

|---|---|---|

| VDD Open | 0.1 fF < Copen < 2 μF | VDD SA-0 , O/P SA-0 |

| VSS Open | 0.1 fF < Copen < 2 μF | VSS SA-1, O/P SA-1 |

| A open | Copen< 10 fF | Wired-And / Wired-Or |

| A shorted to VDD | Rshort < 500 Ω | A SA-1 |

| A shorted to VSS | Rshort < 600 Ω | A SA-0 |

| A shorted to B | Rshort < 200 Ω | Wired-And |

Resistive shorts between signal lines and power/ground lines manifest as SA-1 (shorted to VDD) or SA-0 (shorted to VSS). A radial path as small as 3 nm (between the Cu bumps) or 2 nm (between the RDLs) is sufficient to cause such functional failures. Similarly, a resistive short between two signal wires (e.g., A and B) results in a w-A fault, where both signals are forced to 0 if either one is low. This behavior is observed with a radial path of 4 nm (Cu bumps) or 3 nm (RDLs). The defect sizes and their corresponding functional impacts are summarized in Table. III. Any deformities smaller than these thresholds manifest as resistive defects, the analysis of which is left for future work.

IV. BIST Solution

In chiplet-based packages, shorts occur almost 95% times more often than opens [25]. From the fault analysis in Section III, we observe that some opens can be modeled as SAFs while others can be modeled as bridging faults due to coupling. Our BIST solution targets these hard SAFs and bridging faults, focusing on the high-risk areas identified from defect analysis. Testing for parametric faults and defect size estimation is left for future work. Given that FOWLP enables thousands of I/Os for each chiplet [26], test pattern application must be carefully optimized. For instance, when testing for a short defect, applying alternating test patterns is required for the interconnect group under test (GUT).

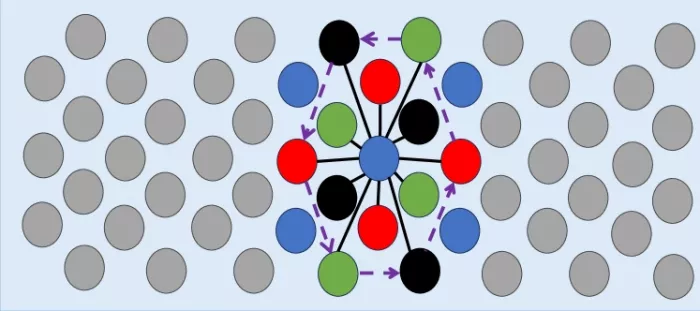

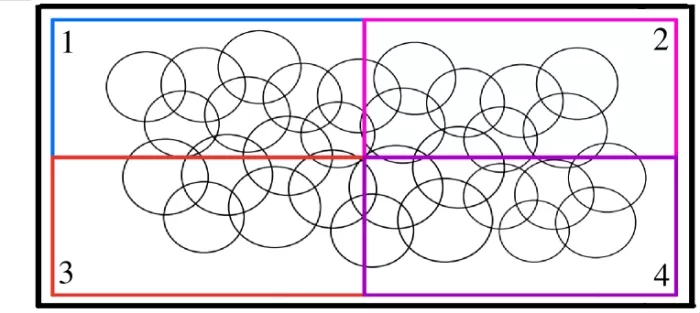

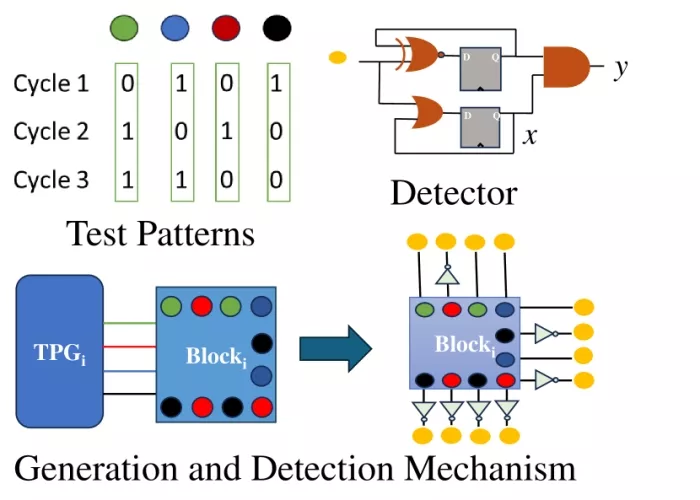

The arrangement of Cu pillars (rectangular or hexagonal) affects the probability of shorts between these bumps. From [17], we know that in a hexagonal configuration, each bump can potentially short to any of its 12 adjacent bumps, as illustrated in Fig. 6(a). By modeling this as a graph coloring problem, it has been shown that only four distinct codewords are needed to test these 12 faults. Now consider a GUT (represented as a circle in Fig. 6(b)) containing 13 bumps. Within this GUT, each bump has the potential to short with multiple neighboring bumps. Each bump on the bump map generates its own “circle" of potential shorts. These individual circles overlap because a single bump can be part of multiple circles (or GUTs), resulting in a complex, interconnected web of overlapping circles. To achieve high fault coverage and diagnostic resolution, we must test all these overlapping GUTs simultaneously. However, this task becomes more challenging as the number of I/Os grows. This is because each bump requires a dedicated detector circuit, resulting in increased area overhead. Additionally, signals from the test pattern generator (TPG) must route to numerous bumps, causing congestion.

To address these issues, we propose dividing the bump map into several smaller blocks. Each bump within a block will receive specific test patterns. For shorts that may occur at the boundary between two blocks, we mitigate interference by setting the patterns of the blocks not currently being tested to all 0s. This ensures that any short between blocks will cause the affected bump within the active block to produce an error.

(a)

(b)

Figure 6: (a) Potential bridging map (solid) for single bump [18] and illustration of a GUT (dashed) (b) Block-level division for testing.

IV-A. Detection and Diagnosis

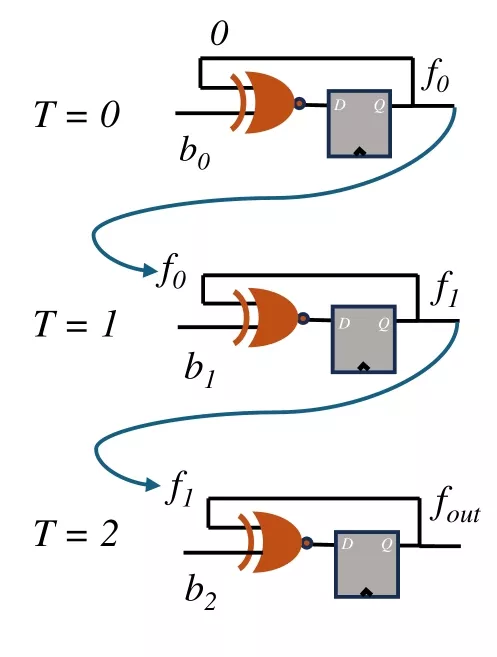

Since distinct test patterns need to be applied to only four colored bumps in a GUT, detecting faults within these selected bumps ensures comprehensive testing of the entire GUT. We next show that three test patterns, as illustrated in Fig. 7(a), can detect all shorts and SAFs among these bumps. It is important to note that the input patterns for the green (blue) and black (red) bumps complement each other. Therefore, a detection circuit designed to identify faults in the green (blue) bumps can detect faults in the black (red) bumps. Fig. 7(a) presents the detector in both the green and blue bumps. By adding an inverter, the faults in the black and red bumps can also be tested. To analyze the test results, we consider two terminals of this detection circuit: x and y. If no faults are present in the interconnects, the output will match the input signals sent from the driver side. However, if a bridging fault occurs between the bumps, the received signals will be erroneous.

(a)

(b)

Figure 7: (a) Test patterns and detection circuit (b) Response analysis.

Let the incoming bits to the detection circuit at time steps T=0, T=1, and T=2 be b0, b1, and b2, respectively. The corresponding outputs at these time steps are f0, f1, and fout; see Fig. 7(b). It can be seen that the output of the first stage, denoted as f0, is b0′ and b2 must equal f1 to ensure that fout=1. Moreover, when b0=0, b1 and b2 must be equal (00 or 11) whereas b0=1, b1 and b2 needs to alternate (01 or 10) to yield fout=1. However, in the case when all of them are 0, the OR loopback path enforces fout = 0. Thus, the set of inputs that makes the output 1 is {011, 110, 101}.

Theorem 1. The three test patterns shown in Fig. 7(a) can detect all SAFs and bridging faults associated with interconnects between chiplets. In addition, these patterns can distinguish between any pair of faults with an accuracy of 95.61%.

Proof. We enumerate all faulty responses in Table IV.

SAFs: A SA-0 fault in any interconnect results in an all-0 response, making both x and y equal to 0. In contrast, a SA-1 fault causes y to remain 0 while x becomes 1. Bridging defects manifest as paired faults for adjacent bumps. SA-1 faults can be differentiated from bridging defects when a single faulty response is observed.

TABLE IV: Fault detection scenarios.

| Faults | b0b1b2 (w-A) (w-O) |

Response (x, y) (Bump1) (Bump2) |

Detection Outcome |

|---|---|---|---|

| SA-0 | 000 | (0, 0) | Detected |

| SA-1 | 111 | (1, 0) | Detected |

| Green + Blue | (001) (111) |

(1, 0) (1, 0) (1, 0) (1, 0) |

Detected in both |

| Green + Red | (010) (011) |

(1, 0) (1, 1) (1, 1) (1, 0) |

Detected in one bump |

| Green + Black | (000) (111) |

(0, 0) (1, 0) (1, 0) (0, 0) |

Detected in both |

| Blue + Red | (000) (111) |

(0, 0) (1, 0) (1, 0) (0, 0) |

Detected in both |

| Blue + Black | (100) (101) |

(1, 0) (1, 1) (1, 1) (1, 0) |

Detected in one bump |

| Red + Black | (000) (110) |

(1, 0) (1, 0) (1, 0) (1, 0) |

Detected in both |

Green Bump: If the green bump is shorted with blue bumps, w-A and w-O generate 001 and 111, respectively. In both cases, y is 0 while x remains 1, thus detecting the fault. When the green bump is shorted with the red bump, w-A produces 010, which matches the fault-free response for the red bump; the fault is only detected at the y terminal of the green interconnect. Conversely, w-O produces the opposite effect. Lastly, when shorted with the black bump, the response is either all 0 or all 1, depending on the wired operation, and this fault is detected at both bumps (y=0).

Blue Bump: A short between blue and red bumps can be analyzed as above. When blue is shorted to black, w-O produces a 101 signal, which is the nominal pattern for the blue interconnect. As a result, the fault is not detected at y. However, it is still identified in the black interconnect. The w-A model results in the opposite outcome.

Red Bump: For red and black interconnects, w-A returns all-0, which is easily detected. The w-O operation generates 110; an inverter before the detection circuit converts 110 to 001, allowing the fault to be detected.

Figure 8: Design of the control circuit for test pattern application.

There are two scenarios where the erroneous y-value is only observed in one bump. Take the w-A case for the green and blue bridging fault. The (x,y) pair for the green bump is identical to that of a green SA-1 fault. Therefore, it is impossible to differentiate between a green SA-1 fault and a green-red bridging fault. There are three additional indistinguishable fault pairs: (blue SA-1, blue+black), (red SA-1, green+red), and (black SA-1, red+black). The total number of faults consists of 8 SAFs and 6 bridging faults. The diagnosability D is therefore given by

Even when a fault is not diagnosable, it is detected in at least one bump. By rerouting one of the signals to a spare bump, we can avoid discarding the package. The detected faults can be mapped to Table III and Fig. 4 to deduce the range of defect size and deformities in chiplet interconnects.

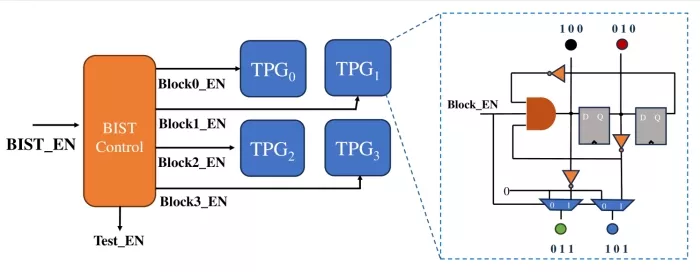

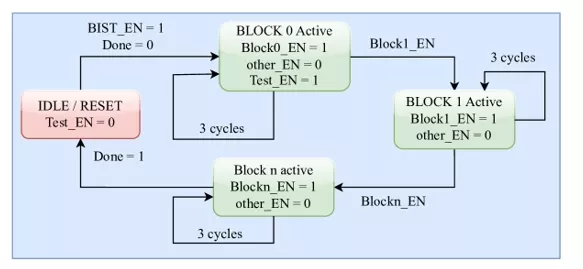

IV-B. Control Architecture and PPA Assessment

The BIST control circuit is shown in Fig. 8. Upon activation of the BISTEN signal, the finite state machine (FSM) transitions from the IDLE state and activates the TestEN signal. The FSM starts to iterate from the IDLE state to enable all the blocks one by one; refer to Fig. 9. For each block, the FSM generates a BlockEN signal that initiates generating patterns for all four colored bumps. All GUTs in a block can share the same TPG and receive the corresponding test patterns for each colored bump. The FSM further guarantees that blocks not under test are set to receive a zero signal by setting the other BlockEN signals to a low state. Two MUXes in the generator circuit ensure that when BlockEN is low, the bumps of that block receive a 0 signal. Furthermore, all blocks can be tested sequentially by applying the same BISTEN signal at the receiving end. One BISTEN signal can be used for each I/O interface to synchronize block-by-block testing, supporting communication in both directions.

Figure 9: Block diagram of the FSM for BIST control.

To evaluate PPA impact, we considered the AES and DES OpenCore benchmarks. Two copies of each core were combined by feeding the output of the first core into the input of the second, forming two hypothetical multi-chiplet packages. AES has a higher I/O count (128), while the DES is larger, with half the number of interconnects. For each design, we considered two test scenarios. In the first scenario, the interface is divided into two blocks. For AES, two test pattern generator (TPG) blocks drove test patterns to 64 I/Os (32 for the DES package), while 64 (32) detectors were used on the receiving side. The detectors can be shared between blocks to optimize area, and a MUX selects the appropriate response signals based on the specific BlockEN data.

TABLE V: PPA analysis for different configurations.

| Parameter | AES | DES |

|---|---|---|

| Clock frequency | 666.67 MHz | 1 GHz |

| Nominal Area (µm2) 2-Block BIST-ed 4-Block BIST-ed |

40231 42211 ( 4.92%) 41677 ( 3.6%) |

66693 67618 ( 1.39%) 67842 ( 1.73%) |

| Nominal Power (mW) 2-Block BIST-ed 4-Block BIST-ed |

12.81 13.66 ( 6.6%) 13.29 ( 3.75%) |

57.19 57.86 ( 1.15%) 58.1 ( 1.57%) |

In the second scenario, the I/Os were divided into four blocks, each with 32 (16) I/Os and 32 (16) detectors. This setup required the deployment of four TPG blocks. For both test cases, we synthesized the designs using the 45 nm Nangate standard cell library; the results are shown in Table V.

Transitioning from a 2-block to a 4-block configuration for AES leads to a reduction in both power and area overhead. However, note that while the 4-block configuration is more PPA-efficient, it results in increased test time (due to sequential testing) compared to the 2-block configuration. The DES case study involves fewer I/Os. Although the detector circuits are fewer, more TPG blocks leads to more control circuits, and the combinational circuit requirement becomes dominant, increasing area overhead. The total area overhead is proportional to the number of I/Os per interface; adding more blocks becomes beneficial as the number of I/Os increases.

V. Conclusion

We have presented a defect analysis framework for FOWLP and demonstrated how these defects can be mapped to their corresponding faulty circuits. Through fault simulation on a test package in HSPICE, we illustrated what level of deformities can lead to catastrophic functional failures. Additionally, we introduced a BIST architecture that achieves full fault coverage using only three test patterns while also providing fault diagnosis with over 95% accuracy. Results for two benchmarks highlight how design decisions can be optimized with respect to PPA and test time constraints.

Acknowledgment

This research was supported in part by the National Science Foundation in part by CHIMES.

References

[1] J. H. Lau, “Recent advances and trends in advanced packaging,” IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 12, no. 2, pp. 228–252, 2022.

[2] S. Li et al., “High-bandwidth chiplet interconnects for advanced packaging technologies in AI/ML applications: Challenges and solutions,” IEEE Open Journal of the Solid-State Circuits Society, 2024.

[3] S. Chen et al., “The survey of chiplet-based integrated architecture: An eda perspective,” arXiv preprint arXiv:2411.04410, 2024.

[4] E. Hudson et al., “Deca & Cadence breakthrough heterogeneous integration barriers with adaptive patterning™,” in IEEE 71st Electronic Components and Technology Conference (ECTC), 2021, pp. 45–49.

[5] L. Lee et al., “Fowlp technology as wafer level system in packaging (SiP) solution,” in International Conference on Electronics Packaging (ICEP), 2017, pp. 491–493.

[6] C. C. Liu et al., “High-performance integrated fan-out wafer level packaging (InFO-WLP): Technology and system integration,” in International Electron Devices Meeting, 2012, pp. 14–1.

[7] S. Wang et al., “Warpage analysis and prediction of the advanced fan-out technology based on process mechanics,” IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 11, no. 12, pp. 2201–2213, 2021.

[8] M. Z. Ding et al., “Molding process development for high density I/Os fan-out wafer level package (FOWLP) with fine pitch RDL,” in IEEE 18th Electronics Packaging Technology Conference (EPTC), 2016, pp. 13–18.

[9] J. H. Lau et al., “Warpage and thermal characterization of fan-out wafer-level packaging,” IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 7, no. 10, pp. 1729–1738, 2017.

[10] M.-Y. Tsai, Y.-W. Wang, and C.-M. Liu, “Thermally-induced deformations and warpages of flip-chip and 2.5 d ic packages measured by strain gauges,” Materials, vol. 14, no. 13, p. 3723, 2021.

[11] V. S. Rao et al., “Process and reliability of large fan-out wafer level package based package-on-package,” in IEEE 67th Electronic Components and Technology Conference (ECTC), pp. 615–622.

[12] S. S. B. Lim et al., “Comprehensive study on die shift and die protrusion issues during molding process of mold-1st fowlp,” in IEEE 20th Electronics Packaging Technology Conference (EPTC). IEEE, 2018, pp. 201–205.

[13] J. Lau et al., “Reliability of fan-out wafer-level packaging with large chips and multiple re-distributed layers,” in IEEE 68th Electronic Components and Technology Conference (ECTC), 2018, pp. 1574–1582.

[14] Y.-C. Lee et al., “Development and validation of a semi-analytical model for predicting asymmetric warpage of fan-out reconstituting packaging,” in 16th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), 2021, pp. 123–126.

[15] “Heterogeneous integration roadmap 2023, chapter 17.”

[16] C. Cui, T. Xu, H. Fu, and J. Huang, “Physical-aware interconnect testing and repairing of chiplets,” in IEEE European Test Symposium (ETS), 2023, pp. 1–4.

[17] P.-Y. Chuang et al., “Generating test patterns for chiplet interconnects with optimized effectiveness and efficiency,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2024.

[18] T.-H. Wang et al., “Test and repair improvements for UCIe,” in IEEE European Test Symposium (ETS), 2024, pp. 1–6.

[19] F. Sheikh et al., “2.5D and 3D heterogeneous integration: Emerging applications,” IEEE Solid-State Circuits Magazine, vol. 13, no. 4, pp. 77–87, 2021.

[20] B. San Jose et al., “Integrating chiplets using chips first ultra-high-density fan-out with maskless laser direct imaging and adaptive patterning for high performance computing,” in IEEE 73rd Electronic Components and Technology Conference (ECTC), 2023, pp. 271–276.

[21] B. Rogers, C. Scanlan, and T. Olson, “Implementation of a fully molded fan-out packaging technology,” in IWLPC, 2013, pp. S10–P1.

[22] C.-W. Kuo and H.-Y. Tsai, “Thermal stress analysis and failure mechanisms for through silicon via array,” in 13th InterSociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, 2012, pp. 202–206.

[23] A. Vangai et al., “Comprehensive defect monitoring technique for advanced fanout packaging process,” in IEEE 19th Electronics Packaging Technology Conference (EPTC), 2017, pp. 1–4.

[24] P. E. Cottrell and E. M. Buturla, “VLSI wiring capacitance,” IBM Journal of Research and Development, vol. 29, no. 3, pp. 277–288, 1985.

[25] S. Chakravarty, “Special session: A call to standardize chip-let interconnect testing,” in IEEE 40th VLSI Test Symposium (VTS), 2022, pp. 1–3.

[26] J. Azémar, “Fan-out wafer-level-packaging: Market and technology trends,” in International Symposium on Microelectronics, vol. 2016, no. 1, 2016, pp. 000 176–000 179.

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- High-Bandwidth Chiplet Interconnects for Advanced Packaging Technologies in AI/ML Applications: Challenges and Solutions

- Development and Optimization of Fine-Pitch RDL for RDL Interposer, and Embedded Bridge Die Interposer Fabrication Using Fan-Out Wafer-Level Packaging Technology

- Fast and Accurate Jitter Modeling for Statistical BER Analysis for Chiplet Interconnect and Beyond

- A physics-constrained and data-driven approach for thermal field inversion in chiplet-based packaging

Latest Technical Papers

- Mapping Space Exploration for Multi-Chiplet Accelerators Targeting LLM Inference Serving Workloads

- Escaping Flatland: A Placement Flow for Enabling 3D FPGAs

- 3D optoelectronics and co-packaged optics: when solving the wrong problems stalls deployment

- Expert Streaming: Accelerating Low-Batch MoE Inference via Multi-chiplet Architecture and Dynamic Expert Trajectory Scheduling

- WarPGNN: A Parametric Thermal Warpage Analysis Framework with Physics-aware Graph Neural Network