Chiplets drive new automated design tools at Leti

By Nick Flaherty, eeNews Europe (June 26, 2024)

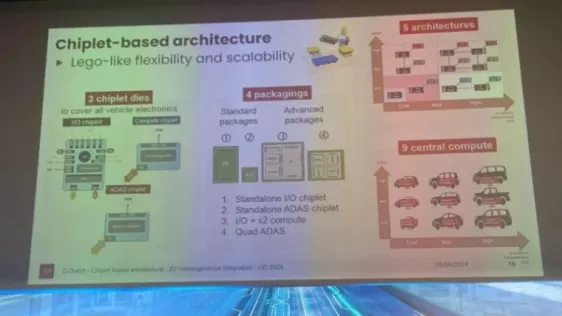

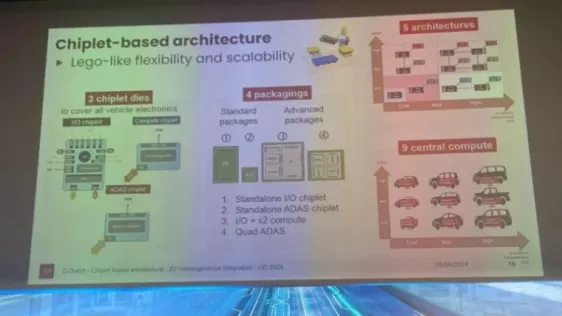

CEA-Leti has shown a scalable chiplet architecture for automotive and developed new automated tools for design exploration.

CEA-Leti has shown a scalable chiplet architecture for automotive and developed new automated tools for design exploration.

The move to software defined vehicles and zonal architectures is also driving the need for chiplets and new design tools at French research group Leti in Grenoble.

“Two years ago we started a feasibility study with a big automotive OEM to define and specify the high level architecture of E/E architectures and at that time there were only two solutions: a SDV based on a GPU and a discrete solution,” said Denis Dutoit, programme manager for advanced computing and chiplets at CEA-Leti.

This chiplet architecture was described at the Leti Innovation Day today.

“This architecture will require a new design methodology as the design space is so huge the traditional way of designing system is no longer valid,” he said.

To read the full article, click here

Related Chiplet

- Interconnect Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Bridglets

- Automotive AI Accelerator

- Direct Chiplet Interface

Related News

- Chiplets diary: Three anecdotes recount design progress

- Why chiplets will transform electronic system design

- CEA-Leti Develops Active Optical Interposers to Connect Chiplets

- Chiplets: Revolutionizing Semiconductor Design and Manufacturing

Latest News

- Where co-packaged optics (CPO) technology stands in 2026

- Qualcomm Completes Acquisition of Alphawave Semi

- Cadence Tapes Out UCIe IP Solution at 64G Speeds on TSMC N3P Technology

- Avnet ASIC and Bar-Ilan University Launch Innovation Center for Next Generation Chiplets

- SEMIFIVE Strengthens AI ASIC Market Position Through IPO “Targeting Global Markets with Advanced-nodes, Large-Die Designs, and 3D-IC Technologies”