Heterogeneous FPGA chiplet implemented in 12nm

The EBRICK-FPGA is a heterogeneous FPGA chiplet implemented in 12nm.

Connectivity Features

| Protocol | Quantity |

|---|---|

| CLINK (128gbps) | 1 |

| UART | 2 |

| I2C | 2 |

| GPIO | 64 |

| ETH 10/100/1000 | 1 |

| SDIO | 1 |

| SPI | 2 |

| QSPI | 1 |

| JTAG | 1 |

| PWM | 1 |

Additional data available! Features, portability, process node, and more can be viewed by logging in with your Chiplet Marketplace account.

- See the entire Heterogeneous FPGA chiplet implemented in 12nm datasheet

- Get in contact with Heterogeneous FPGA chiplet implemented in 12nm Supplier

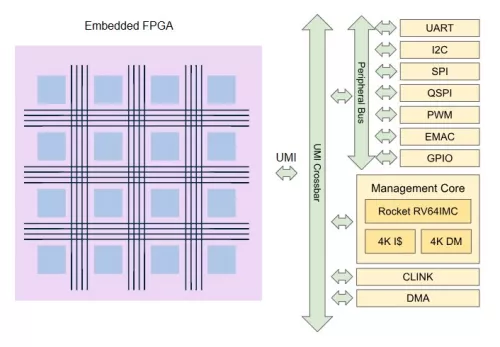

Block Diagram

Related Chiplets

- Machine learning accelerator chiplet implemented in 12nm

- Quad-core 64-bit RISC-V ISA, dual-issue, in-order application class processor chiplet implemented in 12nm

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Active silicon interposer integrating networking functionality, 3D CLINK chiplet interfaces, and 2D UCIe chiplet interfaces

- FPGA Chiplets with 40K -600K LUTS

- Direct Chiplet Interface