Open Chiplet Architecture

By OCA (Open Chiplet Architecture)

1. INTRODUCTION

Chiplets are small, specialized silicon chips designed to function as individual components. Integrated in a System in Package (SiP), chiplets deliver the same functionality as a traditional monolithic chip. Unlike a traditional silicon chip, which combines all functions on a single die, chiplets are fabricated separately and assembled later. This modular approach allows for greater flexibility, improved yield, higher cost efficiency, and shorter time to market. However, despite the benefits, chiplets face interoperability challenges especially when sourced from different vendors. The following table outlines these challenges across various domains.

| Domains | Challenges |

| Interconnect | Chiplets need to establish correct connections and efficient communication across all layers including physical, transport, and protocol. |

| Addressing | Independent address mapping across chiplets complicates scenarios where one chiplet needs to access another chiplet’s resources. |

| Boot | Boot dependencies between chiplets require cross-vendor alignment on communication protocols, boot configuration, and boot flow coordination. |

| System Management | Timely servicing system management commands and managing control loops across chiplets present significant coordination and communication challenges. |

| Security | Variations in chiplet security architectures, such as security-domain partitioning and lifecycle control, create integration challenges and potential vulnerabilities. |

| Interrupts | Inconsistent interrupt implementations across chiplets complicate cross-chiplet interrupt delivery and handling. |

| FuSa and RAS | Ensuring FuSa and RAS interoperability across chiplets is challenging due to architectural diversity and the need for inherently robust solutions. |

| Debug and Test | Debug and test support across chiplets is complicated by the lack o f uniform access ports and inconsistencies in triggers, timestamps, and trace mechanisms. |

| Software | Software interoperability across chiplets is hindered by vendor-specific hardwaresoftware interfaces and inter-software communication protocols. |

2. MOTIVATION

The Open Chiplet Architecture (OCA) is designed to achieve full interoperability among chiplets from different vendors, making them truly ‘plug-and-play’ within a single package. Ultimately, OCA aims to foster an open chiplet ecosystem where chiplet designers can access IPs with well-defined, interoperable interfaces, and package integrators can assemble System-in-Packages (SiPs) using chiplets from various sources. This complements traditional silicon design by also empowering package integrators to participate in chip innovation through integration.

3. OPEN CHIPLET ARCHITECTURE

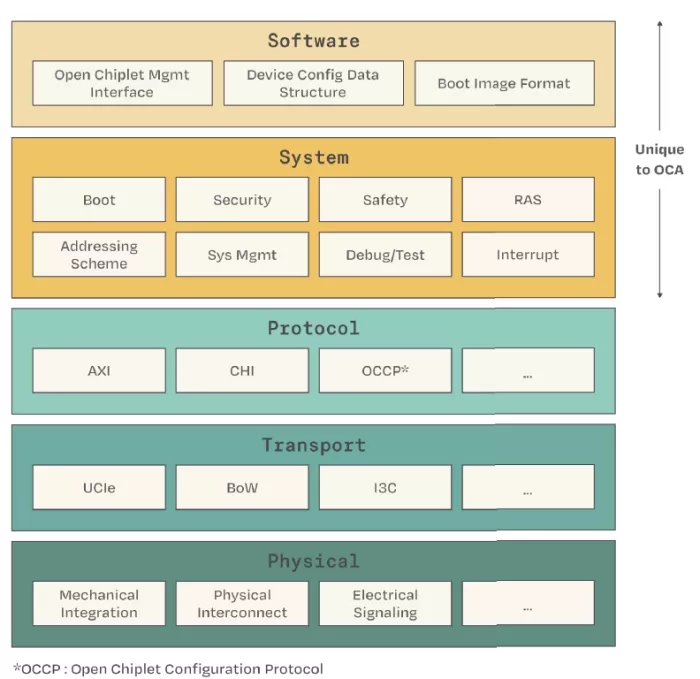

The OCA specification is structured into five layers to support plug-and-play chiplet integration. From top to bottom, these are Software Layer, System Layer, Protocol Layer, Transport Layer, and Physical Layer. Each layer abstracts the one below it, allowing flexibility and avoiding dependence on specific lower-layer solutions.

3.1 A Layered view of OCA

Figure 1 illustrates more details of the 5 layers of OCA definition.

Figure 1 – Layered View of Chiplet Interoperability

At the Software Layer, OCA defines the Open Chiplet Management Interface (OCMI) to standardize inter-chiplet software communication for system and security management. It also specifies a standardized signed image format, enabling a bootloader from one vendor to load signed software from another. Additionally, OCA establishes a standard data structure to provide a comprehensive view o f device configuration within an SiP.

At the System Layer, OCA defines how chiplets collaborate on various system-level features. It introduces the concept of primary and secondary chiplets, organized in a tree or rooted graph structure. The primary chiplet is responsible for loading software and configuring secondary chiplets. A boot flow is standardized with support for separate ownership of individual chiplets and the overall SiP. To integrate independently-designed on-chip networks, OCA defines address translation and traffic routing rules that enable global access to local resources while avoiding fabric deadlock. A system management hierarchy is also specified, in which commands and budget allocations flow downward, while status updates and telemetry flow upward. Additionally, OCA introduces a hardware-assisted time synchronization mechanism to ensure monotonic time progression from software’s perspective. For security, OCA mandates the use of Static Security Identifier (SSID) and Dynamic Security Identifier (DSID) in bus protocols to align chiplet-level security domains. It also specifies secure lif ecycle control across different chiplets, ensuring isolation of proprietary assets while enabling smooth development and Return Merchandise Authorization (RMA) processes. For post-package debug and testing, OCA incorporates IEEE Std 1838 for serial test access. It also standardizes cross-triggering interfaces and networks. For chiplets requiring Functional Safety (FuSa) and Reliability, Availability, and Serviceability (RAS) features, OCA defines standard mechanisms for error interrupt and message delivery.

At the Protocol Layer, OCA specifies inter-chiplet communication protocols, leveraging broadly adopted open standards while taking into account factors like memory coherence, traffic types, D2D communication efficiency. Additionally, OCA introduces the Open Chiplet Configuration Protocol (OCCP), which runs over the side-band transport mechanism. OCCP facilitates chiplet collaboration f or boot, system management, and some domain specific applications.

At the Transport Layer, OCA specifies how data is transferred between chiplets. It adopts UCIe and BoW as the high-speed transport options due to their high bandwidth, low latency, scalability, and efficiency. OCA specifies I3C and I2C as auxiliary transport options. With multi-drop support and in-band interrupts, I3C/I2C offer scalable support for boot configuration, firmware image distribution, status reporting, and multi-chiplet management.

At the Physical Layer, OCA defines the fundamental requirements for chiplet integration to ensure they can be physically ‘plugged’ together. This includes packaging requirements for mechanical integration, physical interconnects, electrical signaling, and power delivery. Chiplet designers choose the integration type (2D, 2.5D, or 3D), while OCA standardizes key aspects for each, such as chiplet placement, die-todie (D2D) interface integration, signal routing, clock distribution, and thermal management. These standards ensure interoperability and reliability across diverse packaging technologies.

3.2 OCA Profiles

OCA defines profiles as refinements of the above base definition through the selection of extensions and the assignment of parameter values, tailored for specific families of chiplets. For example, OCA currently includes the Data Center Profile and the Automotive Profile. To prevent fragmentation, adopters must support all mandatory components of the implemented profile.

3.3 Design Principles

OCA is defined based on the following principles:

| Principles | Description |

| Open | OCA is an open standard that relies solely on open-standard technologies to prevent vendor lock-in. |

| Industry-Standard Based | OCA leverages existing industry standards wherever possible. |

| Accessible | OCA enables integration of commonly available IPs according to the chiplets designer’s needs. |

3.4 Integration Examples

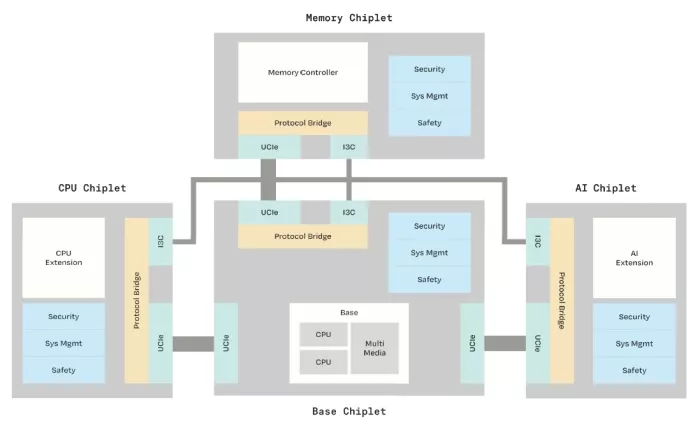

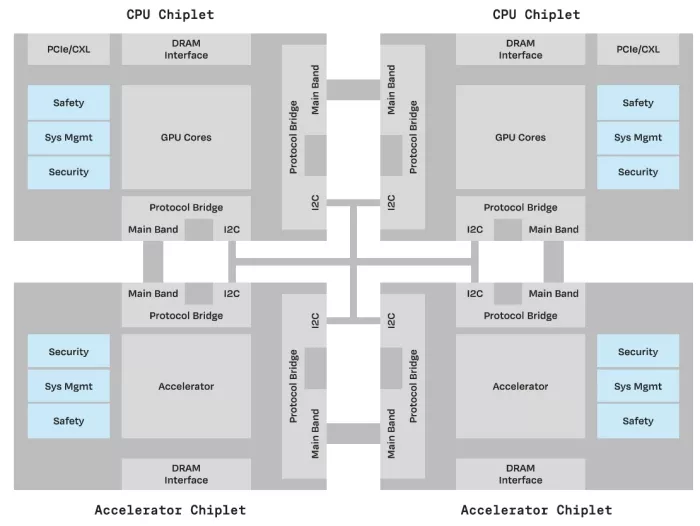

Figure 2 and Figure 3 illustrate two SiP integration examples based on the OCA specification, with OCA defined components color-coded for clarity.

Figure 2 shows an SiP composed of chiplets from multiple vendors, where all interoperability-related components strictly adhere to the five-layer OCA specification.

Figure 2 – Inter-vendor chiplet Integration with a Central Base Chiplet

Figure 3 illustrates an SiP integrating in-house chiplets from the same organization. The So ftware and System Layers follows OCA specification, while the D2D communication protocols and transport mechanisms are proprietary solutions.

Figure 3 – In-house Chiplet Integration that only adopts the OCA Software and System layers

GLOSSARY

| AXI | Bus protocol |

| BoW | Bunch of Wires |

| CHI | Coherent Hub Interface |

| D2D | Die-To-Die - Block that provides the data interface between to silicon dies. |

| DSID | Dynamic Security Identifier |

| I3C | Improved Inter-Integrated Circuit – Enables communication between chips. |

| MSI | Message Signaled Interrupt |

| OCA | Open Chiplet Architecture |

| OCCP | Open Chiplet Configuration Protocol |

| OCMI | Open Chiplet Management Interface |

| OCSP | Open Chiplet Safety Protocol |

| QoS | Quality of Service |

| FuSa | Functional Safety |

| RAS | Reliability, availability, serviceability |

| RMA | Return Merchandise Authorization |

| SiP | System in Package |

| SSID | Static Security Identifier |

| UCIe | Universal Chip Interconnect Express – Open spec for die-to-die interconnects. |

The Open Chiplet Architecture has been developed by Tenstorrent as an open standard.

Related Chiplet

- Interconnect Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Bridglets

- Automotive AI Accelerator

- Direct Chiplet Interface

Related Technical Papers

- A Heterogeneous Chiplet Architecture for Accelerating End-to-End Transformer Models

- Gemini: Mapping and Architecture Co-exploration for Large-scale DNN Chiplet Accelerators

- Universal Chiplet Interconnect Express: An Open Industry Standard for Memory and Storage Applications

- Resister: A Resilient Interposer Architecture for Chiplet to Mitigate Timing Side-Channel Attacks

Latest Technical Papers

- LaMoSys3.5D: Enabling 3.5D-IC-Based Large Language Model Inference Serving Systems via Hardware/Software Co-Design

- 3D-ICE 4.0: Accurate and efficient thermal modeling for 2.5D/3D heterogeneous chiplet systems

- Compass: Mapping Space Exploration for Multi-Chiplet Accelerators Targeting LLM Inference Serving Workloads

- Chiplet technology for large-scale trapped-ion quantum processors

- REX: A Remote Execution Model for Continuos Scalability in Multi-Chiplet-Module GPUs