Electrothermal co-optimization of 2.5D power distribution network with TTSV cooling

By Yang Wang, Changle Zhi, Gang Dong, Daihang Liu, Deguang Yang & Zhangming Zhu

Xidian University, China

Abstract

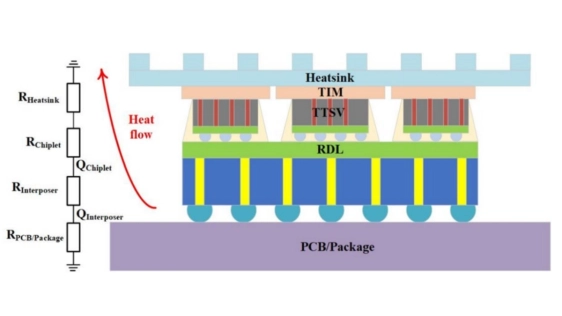

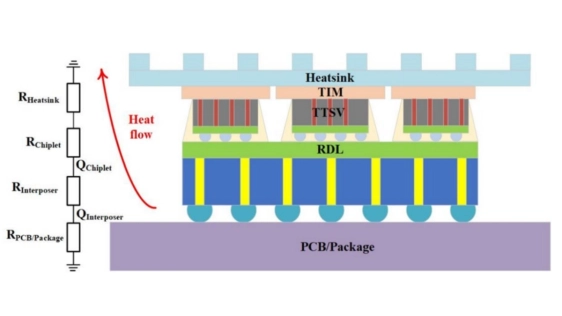

Thermal and power integrity management remains a fundamental challenge in 2.5-dimensional (2.5D) integrated microsystem design. This paper proposes an electrothermal co-optimization design methodology for a 2.5D power distribution network with thermal through silicon via (TTSV) cooling. A hybrid metaheuristic optimization algorithm is presented to optimize the multi-objective function in terms of both the electrothermal properties and manufacturing cost. The proposed approach achieves an optimal solution (minimum fitness value = 310.3) for TTSV scaling and chiplet placement, albeit with increased computational complexity. Compared to the finite element simulation results, the average absolute errors of the impedance and temperature values obtained from the optimization are 3.97 and 0.35, respectively. The proposed method is effective in enhancing thermal management, satisfying power and signal integrity requirements, and minimizing manufacturing costs.

Thermal and power integrity management remains a fundamental challenge in 2.5-dimensional (2.5D) integrated microsystem design. This paper proposes an electrothermal co-optimization design methodology for a 2.5D power distribution network with thermal through silicon via (TTSV) cooling. A hybrid metaheuristic optimization algorithm is presented to optimize the multi-objective function in terms of both the electrothermal properties and manufacturing cost. The proposed approach achieves an optimal solution (minimum fitness value = 310.3) for TTSV scaling and chiplet placement, albeit with increased computational complexity. Compared to the finite element simulation results, the average absolute errors of the impedance and temperature values obtained from the optimization are 3.97 and 0.35, respectively. The proposed method is effective in enhancing thermal management, satisfying power and signal integrity requirements, and minimizing manufacturing costs.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- Co-Optimization of Power Delivery Network Design for 3-D Heterogeneous Integration of RRAM-Based Compute In-Memory Accelerators

- Inter-chip Clock Network Synthesis on Passive Interposer of 2.5D Chiplet Considering Transmission Line Effect

- Thermo-mechanical co-design of 2.5D flip-chip packages with silicon and glass interposers via finite element analysis and machine learning

- Thermal Implications of Non-Uniform Power in BSPDN-Enabled 2.5D/3D Chiplet-based Systems-in-Package using Nanosheet Technology

Latest Technical Papers

- Spatiotemporal thermal characterization for 3D stacked chiplet systems based on transient thermal simulation

- Interconnect-Aware Logic Resynthesis for Multi-Die FPGAs

- Scope: A Scalable Merged Pipeline Framework for Multi-Chip-Module NN Accelerators

- Scaling Routers with In-Package Optics and High-Bandwidth Memories

- TDPNavigator-Placer: Thermal- and Wirelength-Aware Chiplet Placement in 2.5D Systems Through Multi-Agent Reinforcement Learning