3D Electronic-Photonic Heterogenous Interconnect Platforms Enabling Energy-Efficient Scalable Architectures For Future HPC Systems

By Anirban Samanta 1, Shun-Hung Lee 1, Chun-Yi Cheng 2, Samuel Palermo 2, S. J. Ben Yoo 1

1 Department of Electrical and Computer Engineering, University of California, Davis, CA, USA

2 Analog and Mixed Signal Center, Texas A&M University, College Station, TX, USA

Abstract

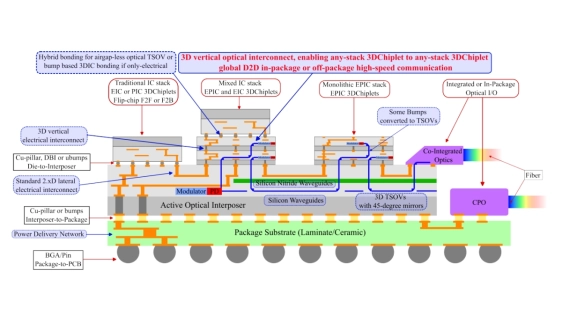

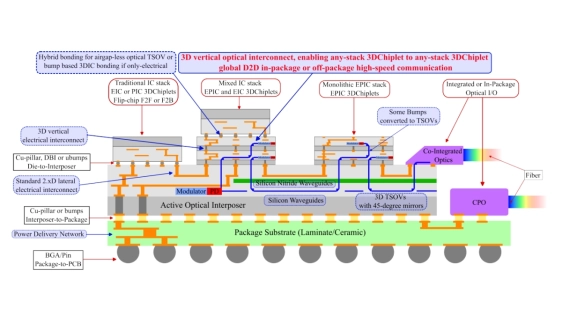

3D interconnects have emerged as a solution to address the scaling issues of interconnect bandwidth and the memory wall problem in high-performance computing (HPC), such as High-Bandwidth Memory (HBM). However, the copper-based electrical interconnect retains fundamental limitations. Dense I/O for high-speed signals lead to degraded signal quality for end-to-end links, necessitating additional circuits to mitigate signal impairments and resulting in poor energy efficiency. We propose a 3D chiplet stacking electronic-photonic interconnect (EPIC) platform, which offers a solution by moving the high-speed data communication interface to the optical domain across the 3D stack by using Through Silicon Optical Vias (TSOV), while retaining the functionality of electrical TSVs and 2.5D interconnects for power delivery and short-reach low-latency communications. We then benchmark the proposed model against state-of-the-art 3D electrical interconnects to demonstrate our 3D EPIC platform beating the 3D electrical interconnects to > 10 TB/s/mm2 bandwidth density. We present a pathway to extend our demonstrated, industry-ready design to achieving ≤ 100 fJ/bit high-speed communication.

3D interconnects have emerged as a solution to address the scaling issues of interconnect bandwidth and the memory wall problem in high-performance computing (HPC), such as High-Bandwidth Memory (HBM). However, the copper-based electrical interconnect retains fundamental limitations. Dense I/O for high-speed signals lead to degraded signal quality for end-to-end links, necessitating additional circuits to mitigate signal impairments and resulting in poor energy efficiency. We propose a 3D chiplet stacking electronic-photonic interconnect (EPIC) platform, which offers a solution by moving the high-speed data communication interface to the optical domain across the 3D stack by using Through Silicon Optical Vias (TSOV), while retaining the functionality of electrical TSVs and 2.5D interconnects for power delivery and short-reach low-latency communications. We then benchmark the proposed model against state-of-the-art 3D electrical interconnects to demonstrate our 3D EPIC platform beating the 3D electrical interconnects to > 10 TB/s/mm2 bandwidth density. We present a pathway to extend our demonstrated, industry-ready design to achieving ≤ 100 fJ/bit high-speed communication.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related Technical Papers

- MFIT : Multi-FIdelity Thermal Modeling for 2.5D and 3D Multi-Chiplet Architectures

- System-Technology Co-Optimization for Dense Edge Architectures using 3D Integration and Non-Volatile Memory

- FoldedHexaTorus: An Inter-Chiplet Interconnect Topology for Chiplet-based Systems using Organic and Glass Substrates

- ChipletPart: Scalable Cost-Aware Partitioning for 2.5D Systems

Latest Technical Papers

- Towards Scalable Multi-Chip Wireless Networks with Near-Field Time Reversal

- Hybrid surface pre-treatments for enhancing copper-to-copper direct bonding

- Toward Digital Twins in 3D IC Packaging: A Critical Review of Physics, Data, and Hybrid Architectures

- Foundry-Enabled Patterning of Diamond Quantum Microchiplets for Scalable Quantum Photonics

- Advances in waveguide to waveguide couplers for 3D integrated photonic packaging