Synopsys looks to AI, 3D die for trillion transistor designs

By Nick Flaherty, eeNews Europe (March 21, 2024)

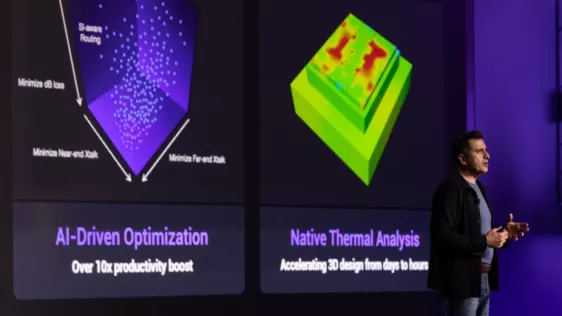

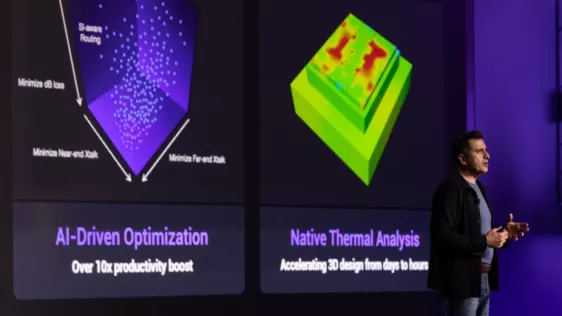

AI boosting the development of multi-die designs will be key to achieving trillion transistor devices says the CEO of design tool pioneer Synopsys.

AI boosting the development of multi-die designs will be key to achieving trillion transistor devices says the CEO of design tool pioneer Synopsys.

“We see three major growth drivers for the industry, said Sassine Ghazi, Ghazi, who took over as CEO of Synopsys from founding CEO Aart de Geus in January this year.

“The rapid acceleration of AI is driving a massive improvement in productivity, not just in our space but in many end markets. Second is the proliferation of silicon. What going to power the AI advancements is the silicon,” he said at this year’s Synopsys User Group (SNUG) meeting which is celebrating its 35th anniversary.

To read the full article, click here

Related Chiplet

- DPIQ Tx PICs

- IMDD Tx PICs

- Near-Packaged Optics (NPO) Chiplet Solution

- High Performance Droplet

- Interconnect Chiplet

Related News

- SEMIFIVE Strengthens AI ASIC Market Position Through IPO “Targeting Global Markets with Advanced-nodes, Large-Die Designs, and 3D-IC Technologies”

- Ansys Enables 3D Multiphysics Visualization of Next-Generation 3D-IC Designs with NVIDIA Omniverse

- Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 Gbps

- SEMIFIVE Collaborates with Synopsys to Develop Advanced Chiplet Platform for High-Performance Multi-Die Designs

Latest News

- Lightmatter Achieves Record 1.6 Tbps Per Fiber to Accelerate AI Optical Interconnect

- Arm Positions Neoverse for AI and Telco Networks at MWC

- NVIDIA Compute Architecture Paves the Way for Scale-Up Optical Interconnects; CPO Penetration in AI Data Centers Expected to Rise Steadily

- CEA-Leti and NcodiN Partner to Industrialize 300 mm Silicon Photonics for Bandwidth-Hungry AI Interconnects

- HyperLight, UMC, and Wavetek Announce Strategic Partnership for High-Volume Foundry Production of TFLN Chiplet™ Platform