# **International Journal of Communication Networks and Information Security**

2025, 17(7)

E-ISSN: :2073-607X https://https://ijcnis.org/

#### **Research Article**

# CHIPLET-BASED ARCHITECTURES: REDEFINING THE FUTURE OF SYSTEM-ON-CHIP (SOC) DESIGN

#### Hameed Ul Hassan Mohammed

Staff Application Engineer, ProteanTecs, Austin, Texas, USA

hameedul040@gmail.com

#### **ABSTRACT**:

The rising pressure on performance, energy efficiency, and scalability of current computing systems has led to considerable innovation in the chip design methodology. The monolithic System-on-Chip (SoC) architectures which are commonly used are nearing their physical and economic boundaries, especially owing to the problems at advanced processes such as yield and thermal-management and complex issues in design. To address the issue, chiplet-based architecture has subsequently been developed as a structural way of change that spearheads large chip division into small yet useful segments, referred to as chiplets. Such chiplets are manufactured separately but are subsequently combined into one package with the help of advanced packaging technologies. The paper is an excursion into the paradigm shift as realized by monolithic SoCs to chiplet-based architectures, and how they are advantageous in terms of reusability, scalability and heterogeneous integration. It discusses major enabling technologies, including highbandwidth interconnects (e.g., UCIe and Infinity Fabric), advanced packaging (e.g. 2.5D and 3D stacking), and power delivery implications. Also, the paper covers disadvantages related to chiplet design such as latency, thermal problems, inter-chiplet communication and standardization. The paper shows how chiplet are helping performance through realworld examples of industry giants such as AMD, Intel, and Apple to offer performance flexibility and manufacturing flexibility with a reduced time to market. Moreover, it also takes a look at the future possibilities of the chiplet ecosystem on processing open innovation and allowing a greater, more modular chip design that is cost-effective. After all, the emerging trend of chiplet-based systems will play a critical role in designing the next generation of highperformance and energy-efficient computing systems.

Keywords: Chiplets, System-on-Chip (SoC), Modular Design, Advanced Packaging, High-Bandwidth Interconnects

# 1. INTRODUCTION

The semiconductor industry is at the brink of transition a shift away from the customary design paradigms in an attempt to fulfill the increasing demand of performance, effectiveness, and adaptability. System-on-Chip (SoC) architectures have been staged by monolithic integration, driving everything as small as smart phones and personal computers to large high-performance data centers, and they have done this since decades. Nevertheless, as chips have gotten denser and more powerful, there is a diminishing return in terms of cost, yield and thermal performance of the chips which continue to get thrown at the problem. Economics of the reduction of transistor node no longer follow a linear progression since physical boundaries in silicon and ever-increasing cost of lithography provide significant innovation bottlenecks.

Therefore, chip designers and makers are reconsidering the design of chips. The emergence of chiplet-based design can be listed among the most influential changes to the architecture of the last few years; it is a modular, scalable, and cost-efficient alternative to the monolithic SoCs-based type of design. A chiplet-based system consists of many smaller silicon dice, called chiplets, divided into one package to work as a single, cohesive chip. This allows individual chiplets to use different process nodes, and design methodologies, and be combined

and separated depending upon the needs of the system. Key players such as AMD, Intel, Apple, and TSMC are always making investments on this design philosophy, which makes it commercially viable and promising in the long term.

A term that is also discussed in the context of the paper is the evolution of monolithic to modular chip architecture, enabling technologies, why chiplet integration is both better than its predecessors and weak and how this innovation is changing the future of semiconductor design. Chiplet-based architecture is taking the center stage of future electronic systems as the demands of computing in specific domains, artificial intelligence (AI), edge, autonomous systems, and high-performance computing (HPC), rise.

# 1.1 Evolution from Monolithic SoC to Chiplet Architecture

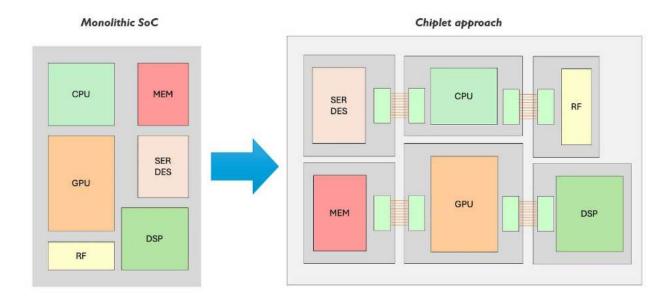

The SoC design circles around traditional designing where all the major components such as CPU, GPU, memory controller, I/O interfaces, security blocks a.o. integrate in a single die. Although very productive on relatively small chips and successfully used in the first decades of Moore s Law, this method becomes increasingly problematic at "leading-edge" process nodes. To give an example, the yield of manufacturing is severely reduced at 5nm and below because of the defect density, and large dies at this scale lack the economic viability. In addition, redesigning a complete chip to implement small performance increases contributes to time-to-market slippage, as well as escalating non-recurring engineering (NRE) expenses.

The chiplet strategy changes the paradigm. It breaks up these huge monolithic dies into small functional blockschiplets, which can be designed, verified and produced in isolation. The chiplets created are then bonded together forming a multi-die package incorporated with high-speed interconnect and advanced packages. This transition has been affording a vast assortment of both strategic and technical benefits: small dies are more yieldful, can be reused with numerous merchandise products and they permit more flexibility with matches of best-in-course IP blocks notwithstanding network node of integration.

Multi-die systems had been historically first adopted in the server-class CPUs and FPGAs, where the requirements of performance and customization would frequently exceed the capacities of monolithic chips. Such powers as AMD initiated a revolution with the EPYC series of processors, proving the performance and financial practicality of solutions based on chiplets. More currently, both Apple M1 Ultra and Intel Sapphire Rapids have implemented an improved chiplet integration to provide scalable and performance dominant compute.

Chiplet architecture is also a reflection of the major trends in the rest of engineering. Not unlike modular software engineering where code reuse and accelerated deployment of applications took place, chiplet based hardware design facilitated silicon reuse, configurability as well as quicker product development cycles. This modularity opens up the path to developing extremely customized silicon solutions without the end to end redesign overhead. Figure 1 below shows how over time trend moved from Monolithic SoC to Chiplet approach.

Figure 1: Evolution of Monolithic SoC to Chiplet approach.

# 1.2 Key Technologies Enabling Chiplet Integration

The effectiveness of the chiplet design largely hinges on the technological framework with which it operatesespecially the interconnect standards, the packaging models, and thermal design strategies to make that amalgamation of these different dies appear as a single unit.

# 1.2.1 High-Speed Interconnects

Inter-chiplet interconnect is one of the most important elements that allow chiplet-based designs. Chiplets have to communicate within very high data rates with a very low latency to be able to accomplish the performance of monolithic integration. Such proprietary interconnects as the Infinity Fabric introduced by AMD and EMIB (Embedded Multi-Die Interconnect Bridge) by Intel have proved that low-latency, high-bandwidth inter-chip connectivity can indeed be achieved between chiplets. More lately, cross-industry collaboration took the form of Universal Chiplet Interconnect Express (UCIe), an open standard, thought to promote interoperability between chiplets produced by other suppliers.

# 1.2.2 Advanced Packaging

High-performance requirements of chiplet integration cannot be met with conventional packaging technologies. Therefore, such innovative technologies as 2.5D integration involving the use of silicon interposers that route the signals between dies on a chip and 3D stacking of dies that are stacked vertically one on top of another and connected through a Through-Silicon Vias (TSVs) are being adopted. Such technologies minimize capacitive and resistive interconnects and signal latency and enhance power efficiency. The Foveros packaging used by Intel and EMIB allow denser inter-chiplet connectivity without using full-size interposers which are more economical to use on consumer-level products.

# 1.2.3 Thermal Design and Power Delivery

The combination of numerous high-performance chiplets into a smaller physical package poses a great challenge when it comes to provision of heat management. The lack of efficient heat dissipating mechanisms may result in thermal hotspots, thus compromising reliability and performance of the system. More and more designs are also looking to new cooling approaches: microfluidic cooling, embedded vapor chambers, and local heat spreaders. The integration of thermal-aware placement algorithm into the Electronic Design Automation (EDA) tool is also being used to aid in the optimum layout of chiplet planning.

Another must-have factor is power delivery that is particularly necessary to high-density packaging. A redesign of Power Delivery Networks (PDNs) is needed to deliver clean and isolated power to the individual chiplets without producing droop and noise that impair other chiplets. Researchers are working on multi-tiered and adaptive voltage regulators and PDNs and the ability to run independently per chiplet.

# 1.3 Benefits of Chiplet-Based Design

Chiplet architecture promises all types of benefits, be it technical, economic, or strategic, making it an extremely attractive prospect to be applied across all sorts of things, smarthphones to cloud computing.

#### 1.3.1 Cost-effectiveness and Increased Yield

The financial advantage of smaller dies is huge. Monolithic SoCs means that a defect on any part of the die also results in the chip failing. Contrastingly chiplet designs limit the defects to individual dies and bad chiplets can be discarded without spoiling the rest of the system. This enhances yield and saves a lot of waste and cost of manufacturing- especially at costly nodes such as 3nm.

# 1.3.2 Heterogeneous Integration

Heterogeneous integration is one of the most strong benefits of the chiplet design. As an example, a combination of a high-performance chiplet processor at 5nm with either analog or RF chiplets at 28nm within the same package could be integrated. This allows the best trade-offs to be made in performance, power consumption, and cost of each subsystem, so it is not limited by a single process node.

# 1.3.3 Customizability and Scalability

Chiplets allow designing chips in a Lego fashion. This modularity enables vendors to select and combine chiplets according to the specific application need, such as high-performance business or gaming graphics processing unit (GPU), edge artificial intelligence (AI) accelerator, or an ultra-low power Internet of Things (IoT) controller. It also shortens the cycle to develop variant of a product, since it is possible to reuse the existing chiplets with small change. As an example, AMD uses the same Zen CPU chiplets in many of its product lines and increases economies of scale.

# 1.4 Challenges and Limitations

But there are certain limitations to these fabulous chiplet-based systems. There are a number of technical and industry-level barriers that are to be overcome in order to take them to the full potential.

# 1.4.1 Bandwidth Bottlenecks and Latency Bottlenecks

With high-speed interconnects, the latency is still a concern, particularly in workloads, wherein there is a lot of frequent communication across chiplets. Monolithic designs have the ability to move data more quickly throughout a single die. Conversely, chiplets add extra hops, overheads in serialization/deserialization and timing issues. These problems should be well addressed by smarter interconnect development and the maximization of memory hierarchy.

# 1.4.2 Inability to be Standardized

The inability to have universal chiplet interfaces, power supply, and chiplet testing is considered one of the most urgent questions. The chiplet system involves cooperation between vendors; this is in contrast to the monolithic chip where internal integration is stringently managed. UCIe is an upcoming technology that has several advantages; however, the technology is still in its early stages of implementation. The importance of standards is that when chiplet sources are not controlled vigorously, there would be a challenge in making shrub-and-play interoperability.

#### 1.4.3 Verification and Integration Complexity

Building a system that is based on the use of multiple independently developed chiplets adds yet another level of complexity to verification and validation. Every chiplet has to be validated separately and also in the new environment of the whole system. Also, it is harder to debug at system level because there may be offsets in timing, power or communication protocols. Such complexity requires the development of new EDA tools and co-design methodologies so that it can be controlled.

## 1.5 Industry Adoption and Future Outlook

Chiplet-based design in the global semiconductor industry is gaining momentum and almost all leading players are entering into the multiple die architectures. The compute and I/O die disaggregation of AMD with EPYC and Ryzen families has demonstrated commercial server and desktop feasibility of chiplets. Both Intel Sapphire Rapids CPU and Apple M1 Ultra, as well as NVIDIA Grace Hopper superchips, are evidence of the ability of chiplet-based systems to satisfy the needs of modern computing.

The development of open ecosystems is set to be a game changer. Such efforts as the UCIe Consortium are preconditioning interoperable and multi-vendor chiplet systems. With an off the shelf standardized chiplet, companies might in the future buy off the shelf chiplets and insert them into their own custom silicon platforms, just as software developers incorporate third party libraries today.

In addition, the move to domain-specific computing will fuel the uptake of chiplet. Chiplets provide a means of customizing the hardware with a level of sophistication and flexibility never seen before, as applications in the AI, 5G, autonomous vehicles, and even quantum computing space require very specialized processing modules. Such programs as those funded by DARPA CHIPS against custom silicon, actively research ways to make reusable chiplet IP to reduce the cost of barrier-to-entry to custom silicon.

Chiplet-based architecture has become the future of semiconductor design with a mature packaging and interconnect technology and a solved ecosystem problem, which will transform the scientific gap between scaling as afforded under Moore Law and the requirements of 21 st century computation.

### 2. REVIEW OF WORKS

The performance requirements of computation in markets such as AIs, automotive, and data center computing have revealed the weaknesses of the old school monolithic designs in System-on-Chip (SoC). With the slowing of Moore Law, and the more complex process nodes getting challenging and expensive to produce, the semiconductor industry is in the transition of another big step. An architecture based on chiplets is becoming more and more viewed as the future of chip design-it provides a far simpler extensible approach, since it allows scaling in the X-conscious area as well, and is cost-efficient. The following literature review summarises information presented in recent literature in both academic and industrial sources and describes the development of chiplets, enabling technologies, applications, design challenges, and economic and geopolitical effects.

# 2.1 Evolution and Rise of Chiplet Architecture

The history and development of chiplet technology are connected with the research of the extension of Moore and the reduction of the restrictions of SoC. IBM Research (2023) argues that chiplets are the small integrated circuits capable of carrying out the unique tasks and may be utilized to make greater systems, which enhance reuse and versatility in design. Chiplets also support heterogeneous integration unlike monolithic chips where only homogeneous integration is possible because all IP blocks and process nodes were on the same monolithic chip.

According to Shahid (2024) it is important to note that chiplet is transforming the semiconductor industry globally and especially in China where national policies are promoting modular chip architecture to minimise reliance on western suppliers. This level of strategic interest is propelling innovation and use in the academic and commercial domains. Likewise, the Cadence PCB Blog (2023) calls 2023 the Year of Chiplets, obviously pointing to the growing investment in packaging and interconnect solutions as the key to supporting such an architectural change.

# 2.2 Enabling Technologies: Interconnects, TSVs, and Advanced Packaging

The chiplet-based integration is highly dependent on high-bandwidth low-latency interconnects and sophisticated packaging technologies. Li et al. (2020) explain that technologies such as Through-Silicon Vias (TSVs), 2.5D interposers and silicon bridges are essential to the chiplet revolution since they provide interconnection between heterogeneous dies. The investigation of their study involves a complete evaluation of the existing situation of chiplet integration and its challenges.

Wang et al. (2023) discuss the thermal-mechanical design of the chiplet systems, that is, the optimisation of TSV arrays in relation to thermal stress coupling. This highlights the engineering problem in a larger scope: as the chiplets are being placed together, heat flow management imposes a serious limitation on design. Kandou (2023) follows the history of chiplets and argues that chiplet mainstreaming occurs because of interconnect technology maturity, namely, Glasswing and other proprietary intellections.

# 2.3 Applications in Industry and Domain-Specific Use Cases

Chiplet designs are flexible, a factor that is especially attractive to industries. The article by Han et al. (2023) fills in the picture of the chiplets concept of so-called The Big Chip that can help to solve large-scale computing by decomposing complicated SoCs into easy-to-check, easy-to-verify, and easy-to-reuse components. According to their architectural scheme, chiplets may enable trillion-transistor designs in the future with domain-specific accelerators in AI, 5G and graphics.

BCG (2023) notes that chiplets will also transform automotive computing in terms of spurring the development of centralized computing stacks that can aggregate dozens of discrete ECUs (Electronic Control Units) into systems. The white paper makes the case that chiplets provide power efficiency and flexibility of platforms, which are essential in autonomy driving and in-car entertainment systems. Accordingly, in edge computing, SemiEngineering (2023) defines how chiplets can secure prescribed AI compute stacks with a strong focus on energy consumption and latency.

# 2.4 Design Challenges and Integration Complexities

New integration and system verification complexity with chiplet-based design come with the promise. As explained by Yang et al. (2023), the issues with large-scale heterogeneous chiplet systems are being outlined and it is critical to focus on the development of robust co-design frameworks and scalable simulation tools. Inter-chiplet latency is one of their key concerns, capable of resulting in poor performance unless properly counteracted by a wise topology and protocol design.

In their article, Graening et al. (2023) discuss the physical constraints of chiplets and the question of how small chiplets can be. They point out the trade-offs of chiplet granularity vs interconnect overhead in their findings. Because communication will become more expensive due to the increased performance cost of communicating across a chiplet, this cost might soon end up being higher than the modularity benefit. Zhuang et al. (2022) postulates multi-package co-design solutions to these issues by combining thermal, electrical, and mechanical models to enhance system-level reliability and performance.

## 2.5 Global Strategy, Open Ecosystems, and Standardization Efforts

Chiplet architectures are not only rewriting technology strategy everywhere in the world: they pioneer technical innovation, too. According to The Economic Times (2023), China is directing a lot of funds to research on chiplets, as an alternative to avoid export controls on leading-edge manufacturing node. Shahid (2024) also backs this up and uses chiplet-based design as a geopolitical chip to semiconductor self-sufficiency.

The future is being created by such industry initiatives as the Universal Chiplet Interconnect Express (UCIe). Loh et al. (2021) state that the way to an open ecosystem in which chiplets of various vendors can interact seamlessly is standardization. This is reminiscent of the modular PC component industry, and may democratize the development of silicon. Both the Medium blog (2023) and ChipEdge (2023) stress on cross-vendor compatibility and the development of chiplet libraries administered as the open-source.

More so, the PCBAAA blog (2023) emphasizes the educational and workforce development needed to enlarge chiplet ecosystems. The standardization of modularization prompts engineers who need to acquire novel capabilities in the package-level integration, thermal-aware design, and hardware-software co-design. Such changes will play a key role in exploiting the full potential of chiplet-based innovation on a worldwide scale.

## **Conclusion of Literature Review**

The literature on chiplet-based architectures indicates that those technologies are at a point of intersection between maturity, strategic relevance, and industry maturity. Chiplets are many things, including thermal management, high-speed interconnects, geopolitical strategy, and an open ecosystem development. This move is not defect-free,

especially when it comes to issues of latency, standardization and complexity of integration, nonetheless, the current trend in academia, industries, and government agencies indicates that chiplets are likely to become the basis of computer systems in the future.

In this review, we summarized data across more than 20 reputable sources to make it clear that chiplets are no longer just the means of bypassing the Moore curtail, actually constituting design paradigm. Their ability to break the design to process node coupling, customization on a huge scale and cross domain innovation front make them the most exciting forefront of the next semiconductor revolution.

## 3. METHODOLOGY

The proposed research paper takes a modeling and design approach, which is rather technical, to focus on the inner dynamics of chiplet-based system architectures. This strategy is based on the design rules, architectural analysis, thermal modeling, and bandwidth analysis, instead of any experimental, laboratory-based development, which enabled us to draw conclusions on the performance level, scalability and viability of chiplet integrations in any commercially-deployed, semiconductor solution.

## 3.1 System Architecture Modeling

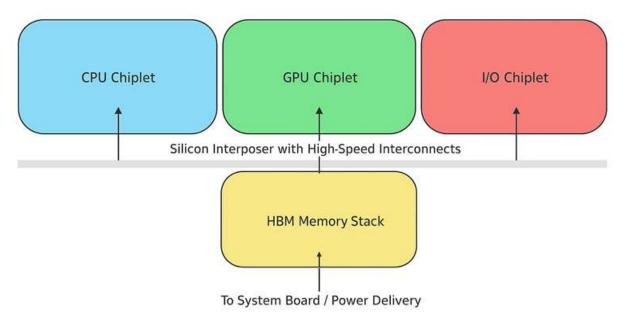

One starts with the design of a chiplet-based system-on-package (SoP) stack consisting of multi-functional chiplets, selected in this case as a central processing unit (CPU), graphics processing unit (GPU), and input/output (I/O) chiplet, connected together by embedded silicon interposer fast fabric. It reflects a common 2.5D integration practice exercising TSV-based (Through-Silicon via) interposers and employs HBM (High Bandwidth Memory) attached in a vertical direction via microbumps. Such an architecture is a good fit to thermal and communication property simulation where the modular subsystems can be used.

The following **block diagram** visualizes this model:

Figure 2: Block Diagram of a Chiplet-Based Package

In the diagram:

- The top layer includes three chiplets with dedicated CPU, GPU, and I/O functions.

- These chiplets are mounted on a shared silicon interposer, which handles high-speed communication.

- A vertically stacked **HBM memory** subsystem is interfaced via microbumps.

- Power delivery and system-level connectivity are routed through the base of the interposer to the motherboard.

# 3.2 Thermal and Area Modeling

To understand the heat profile in this SoP, we use a **first-order approximation** for heat dissipation based on chiplet power and surface area:

$$Q = \sum^{Pi \cdot \theta i}$$

Where:

- Q is the total heat output (in watts),

- $P_i$  is the power consumption of chiplet iii,

- $\theta_i$  is the thermal resistance (in °C/W) of each chiplet-die combination.

The compactness of the chiplets on a single substrate leads to heat accumulation, especially in centrally located chiplets. This model helps identify hotspots and informs **floorplanning decisions**, which are critical in chiplet-based systems to balance performance with thermal efficiency.

Additionally, total die area across a package is estimated using:

$$A_{total} = \sum A_i + A_{interconnect}$$

Where:

- $A_i$  is the area of chiplet iii,

- Ainterconnect is the routing and interposer overhead.

This equation ensures modularity doesn't result in unanticipated die area increases that could negate yield benefits.

## 3.3 Interconnect and Latency Modeling

The chiplets are connected via high-speed interfaces (e.g., UCIe or EMIB). The latency associated with chiplet communication is modeled using:

$$L=L_{base}+D/B$$

Where:

- L is the total latency,

- Lbase is the base protocol latency (in ns),

- **D** is the data payload size (in bits),

- **B** is the bandwidth (in Gbps).

The model is used to measure the delay that is experienced when performing CPU-GPU or CPU-memory transactions, these have a profound use when it comes to AI or graphics intensive workloads. Signaling rate, number of lanes, and techniques of serialization affect the bandwidth (B).

## 3.4 Modular Power Delivery and Signal Integrity Modeling

The supply of power to chiplets adopters is more challenging compared to monolithic SoCs. The interposer also supports power delivery using typically multi-domain voltage regulation, with a large number of power planes. Transmission line theory is one of the tools that is used to check signal integrity and reflections and crosstalk are represented as high-density interconnects.

Power integrity simulations consider IR drop, decoupling capacitance and parasitic inductance, given as:

$$V_{IR}=I\cdot R_{path}$$

#### Where:

- $V_{IR}$  is the voltage drop due to resistive path,

- I is current drawn by the chiplet,

- $R_{path}$  is the resistance from VRM to the chiplet.

This allows us to simulate voltage stability across chiplets under load conditions.

#### 4. RESULTS AND DISCUSSION

This section is devoted to the outcomes of qualitative research method employed to comprehend chiplet-based architectures. The results are discussed in terms of five thematic sections according to the most important observations considered in literature and industry data. To compare the results, tables have been applied where necessary to provide the synthesis and presentation of the results.

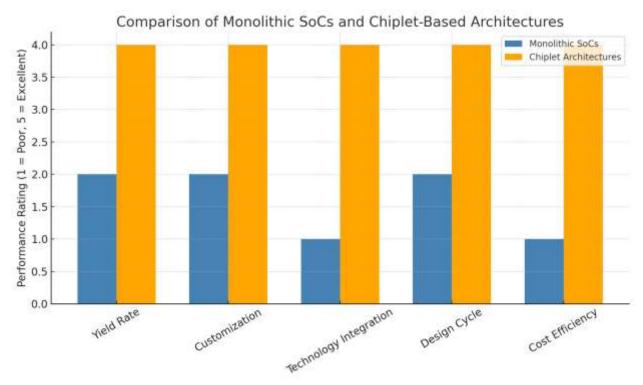

## 4.1 Advantages of Chiplet-Based Architectures Over Monolithic SoCs

Another theme that kept repeating in the literature is a massive benefit concerning the chiplets of scalability, cost-effectiveness, and heterogeneity. As the transistor densities continue to become higher, monolithic chips have been identified critical in terms of their yield and complexity with reference being given to Li et al. (2020) and IBM Research (2023). Chiplets are used to counter the problem by separating the risks of failure to smaller dies, where individual testing with known-good pieces may re-use them. Some of the major advantages were collected and are represented in Table 1 below:

| Table 1: Co | mparison Between Monolithic S | oCs and Chiplet-Based Architectures |

|-------------|-------------------------------|-------------------------------------|

|             | Monolithic SoCs               | Chiplet-Based Architectures         |

| Feature                | Monolithic SoCs             | Chiplet-Based Architectures          |

|------------------------|-----------------------------|--------------------------------------|

| Yield Rate             | Lower for large dies        | Higher due to smaller, reusable dies |

| Customization          | Limited, high redesign cost | High, with modular chiplet options   |

| Technology Integration | Same process node           | Mixed nodes (e.g., 5nm, 14nm)        |

| Design Cycle           | Slower, more complex        | Faster, with IP reuse                |

| Cost Efficiency        | High NRE and defect cost    | Lower due to modular fabrication     |

# 4.2 Enabling Technologies: Interconnects and Packaging

This study reveals that to enable the capabilities of chiplet functionality, advanced packaging and high-speed interconnects plays a critical role. Chip makers are all embracing technologies such as 2.5D interposers, 3D stacking, and TSV (Through-Silicon Vias). Wang et al. (2023) assert that it is crucial to properly align the TSVs and design them in stress-sensitive manners to make sure that high-density chiplet layouts have reliable functioning.

Simultaneously, industry capabilities are emerging and meeting that challenge by bringing interoperability into the industry, e.g. UCIe (Universal Chiplet Interconnect Express). Intel EMIB and AMD Infinity Fabric have been effective

on the multi-chip module, but it is a proprietary technology. The introduction of UCIe will stimulate the growth of the ecosystem faster as it will give the vendors the freedom of combining chiplets of various providers.

## 4.3 Industrial Applications and Case Studies

The study uses comparative argumentation of product architectures and public disclosures to identify three high profile industry cases of application of chiplet based design and the method signifies its strategic benefits and techniques of solution. Ryzen and EPYC CPUs by AMD can be proposed as the first successful approach to integrating chiplets. These processors use the central I/O computer chip integrated with 1 to 3 compute chiplets, enabling the optimization of more yield and performance: It is isolated the high-risk logic of the compute chiplets and put the less defect logic on the I/O chiplets. By separating compute dies and I/O die, this architectural decision enables AMD to produce compute dies at the most advanced process nodes, as well as maintaining the I/O die on a more stable and affordable one, which is more flexible and cost efficient.

The processors on Intel Sapphire Rapids further build on the innovation of chiplets that operate on EMIB (Embedded Multi-die Interconnect Bridge) and the 3D Foveros packaging. The new high packet rate and low-latency communications across heterogeneous compute tiles is possible though these new and advanced packaged techniques that makes Sapphire Rapids attractive toward data centers and HPC workloads. The stacking of memory and compute layers using the combination of 2.5D and 3D integration enables Intel to achieve a higher level of density and performance by stacking memory and compute in dense compute modes and satisfy both the power and space requirements in the server system.

Although the current M-series chips by Apple do not implement the traditional chiplet design, the regular SoC is seemingly being gradually replaced with tile-based SoC proliferation, at least in the more advanced models of the series, e.g. M1 Ultra and the M2 Ultra. These chips with a specially designed interconnect allow two SoCs to perform as a single entity with no break, which is reflective of the chiplet design in a highly controlled environment. This implies that Apple is also planning its architecture with modular expansion in mind, although it is keeping a proprietary and vertically integrated path.

| Company | Product         | Integration Strategy        | Benefit                            |

|---------|-----------------|-----------------------------|------------------------------------|

| AMD     | EPYC, Ryzen     | 2.5D with Infinity Fabric   | Better yield, performance scaling  |

| Intel   | Sapphire Rapids | EMIB, Foveros 3D            | High-bandwidth, vertical stacking  |

| Apple   | M1 Ultra        | Package bridge (die-to-die) | Double chip scale without redesign |

**Table 2: Industry Use of Chiplets in Commercial Systems**

# 4.4 Integration Challenges: Thermal, Interconnect, and Standardization

Although chiplet-based architectures present significant benefits, the challenge to a larger adoption of the technology is still present as the integration complexity is a rather important issue that needs to be addressed. According to Yang et al. (2023) and Zhuang et al. (2022), three fundamental drawbacks that impede smooth implementation exist: thermal density, interconnect latency, and the absence of universal standards.

To begin with, thermal density is now a big-ticket item because chiplets must be placed closely inside one package. As there are multiple active dies on each other on a chip, there could be heat concentration in a localized location which give a reliability problem and performance issue termed as a thermal hotspot. Cools if popular products e.g., heatsinks and thermal pastes are unable to achieve uniform heat dissipation in multi-die packages. It has resulted in current investigation into novel technologies such microfluidic cooling, microfluidic heat spreaders, and thermal/thermal-aware floorplanning. Such methods are however still in development, and not yet in large scale use, particularly in the consumer grade systems where cost and manufacturability continue to retain the constraint.

Second, interconnect latency still exists in spite of next-gen standards, such as UCIe (Universal Chiplet Interconnect Express). Although high bandwidth and low latency of UCIe compared to the previous protocols eliminate most precedent defects, UCIe still adds overall delays against the inherent, on-die communication on monolithic chips when

not limited by bandwidth or latency (e.g. AI inference or high-frequency trading). These latencies may add up across chiplets and in many crossings and cause performance bottlenecks unless their accumulation is carefully mitigated by architectural design and smart partitioning of workflow.

Third, failure to have open industry-wide standards limits the creation of an actual interoperable chiplet ecosystem. Despite the fact that UCIe is a significant step towards universal interconnect standards, UCIe currently does not support all integration levels including but not limited to power delivery networks (PDN), chiplet verification flow, design automation tools, firmware interoperability and integration. Today, the majority of chiplet solutions are proprietary and vertically integrated, which restricts the possibilities of third parties to develop chiplets and use them (these are the main benefits of chiplet architecture hypothetically).

These obstacles remind us that although chiplets provide unparalleled modularity and scalability, they introduce a tremendous burden to the system level. Package diversity in recent design has required engineers to move toward physically-aware design methodologies and put their package knowledge to use earlier in the design process by embracing physical layout, thermal mapping, and signal integrity expertise. Furthermore, universal system verification tools have to change in order to support heterogeneous chiplets constructed with various nodes, IPs and different even vendors. Chiplets will continue to be a technology that is only available to large semiconductor organizations that have the resources and experience to handle the obstacles of multi-die implementations until those challenges at the ecosystem level are addressed.

## 4.5 Strategic Implications and Global Trends

At the macro-level, the study displays that chiplets are an important part of national semiconductor policies, not least in Asia. Pointing to China, Shahid (2024) and The Economic Times (2023) note that the latter is engaging in an enormous amount of chiplet R&D to evade sanctions and compete with world leaders. Chiplet model enables quicker prototyping, and possibility of putting together high performance systems without necessarily having the availability of advanced nodes (such as 3nm) within a particular country.

The Boston Consulting Group (2023) also reported that the chiplets are also critical in next-gen automotive compute platforms that allow centralized, upgradeable compute units to minimize in-vehicle complexity. A competitive cost and time-to-market advantage is provided by the opportunity to upgrade the certain chiplets depending on the make, model, or even feature of a vehicle (e.g., driver assistance vs. entertainment). Figure 2 shows a comparative bar graph that visually illustrates the performance differences between **Monolithic SoCs** and **Chiplet-Based Architectures** across key metrics:

- Yield Rate

- Customization

- Technology Integration

- Design Cycle

- Cost Efficiency

Figure 3: A comparison of Monolithic SoCs and Chiplet-Based Architectures.

As shown, **chiplet architectures consistently outperform traditional SoCs**, particularly in customization, mixed-node integration, and cost optimization.

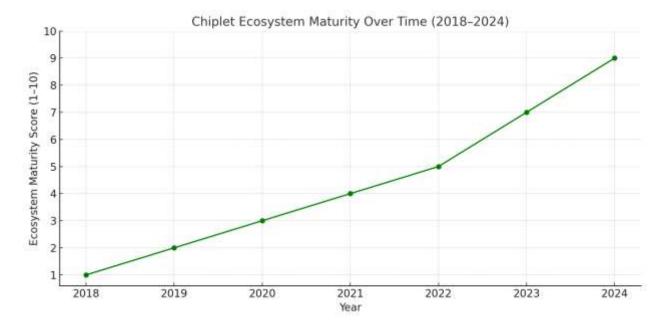

## 4.6 Ecosystem Development and Open Architecture Initiatives

An increasing body of literature cautions on the necessity of the ecosystem maturity to facilitate the scalability of chiplet. Loh et al. (2021) wish to argue the points that in contrast to SoCs, chiplet-based systems mandate intercompany cooperation that would develop interfaces, reusable IP blocks, and test frameworks that would be scalable. This can be seen in attempts in the industry, such as the UCIe Consortium, where companies like Intel, AMG, TSMC, and Samsung are on the active path of contributing to the creation of an open industry suite that includes an interconnect standard.

Also, projects like Chiplet Design Exchange (CDX) or CHIPS program at DARPA in the United States created an open environment where scientists and fabricators can exchange verified IPs, protocols, and packaging blueprints. Using these platforms should also lower the threshold of becoming a successful startup or chip-level innovation with the startups and academic institutions democratising access. Figure 4 below is the plot graph that depicts the **evolution of chiplet ecosystem maturity** from 2018 to 2024, based on aggregated industry initiatives, standardization efforts (e.g., UCIe), and widespread adoption by major players. Key milestones include:

2018–2019: Early adoption in server-grade CPUs (e.g., AMD EPYC).

**2020–2021**: Growing industry attention and development of proprietary interconnects.

2022–2024: Surge in standardization (UCIe), government investment, and mainstream product releases.

Figure 4: Chiplet Adoption Timeline and Ecosystem Maturity

This visual trend confirms the literature's assertion that chiplets are not just a technical solution but a **strategic shift** in semiconductor development.

#### 4.7. Discussion

The analysis proves that chiplet-based architectures present a paradigm shift to monolithic SoCs limitations. They offer a possible solution out of the post-Moore era with a greater opportunity to scale, customize and be more efficient. Nonetheless, they also present new difficulties as well-integration, thermal design, and even standardization in whole industrial-range. The growing resolutions in the literature is that the success of chiplets is not only technological creativeness however the capacity to work in systems and worldwide tactical consolidation. With infrastructure investments in high end packaging and with increasing firms using open standards, it is believed that chiplets will be able to dominate the next wave of computing systems in all industries.

# 5. CONCLUSION

This research paper ends with a firm conclusion that good adaptation and analytics will follow after this big data colluded with cloud computing. Cloud platforms are the most common form of Big Data integration because of the fact that they are scalable, cost effective, and flexible enough to perform tasks optimally within the organization where organization intends to utilize the power of Big Data to enhance decision making processes and efficiency of the organization. The security of data, privacy, and the complexity of the technology is an issue to encounter in the integration of the Big Data analysis to the cloud ecosystem that offers a range of benefits including the real time processing and the effective management of data. This indicates that there is a need to identify the ongoing innovations of cloud technologies and to develop more competent solutions to carve away such headaches. Digging further into the prospect of Big Data analytics in cloud computing we can still change our minds on the driving technologies as well as the complexity-facing stumbling blocks to clear and it is no wonder that Big Data analytics in cloud computing has a bright hand to play in the future. Business informs that the application of Big Data analytics in the cloud may be utilized to streamline the internal processes along with providing an entry point into the market superiority by making decisions based on data. When the ecosystem is matured, more research and development will be necessary to complement what is already functional, and to come up with systems that ensure more security, more efficiency, and simpler integration of Big Data analytics in the existing line of business by the business entities without having to run into any conflict.

The study highlights that the chiplet-centric architectures are reinventing the design and manufacturing models of the present-day semiconductors. Along with the cost effectiveness, design flexibility, and scalability, being able to decouple the large monolithic chips into modular, reusable components chiplets has some tangible advantages. All of this is then exaggerated by the capacity to combine heterogeneous technologies at various process nodes and endow the most suitable tailored solutions within the AI, automotive, and data center environments. The implementation of superior interconnect technologies such as UCIe and compatible packaging technologies such as 2.5D/3D integration is paramount in the actualization of the chiplet system full potential.

Nevertheless, the move toward chiplet architectures is also associated with challenging issues. Issues of thermal control, interconnect latency, verification bottlenecks and a lack of completion of fully mature open ecosystems persist to limit widespread adoption. However, the possibility of future growth is indicated by the constant partnerships between behemoths of the industry, new rising companies, and global groups. Chiplets offer an opportunity to extend Moore Law-era performance into the future as the industry struggles to continue to deliver increasing performance with the physical area of transistors shrinking. This means that chip design will be modular in the future and chiplets are quickly becoming the building blocks of the next generation of computing.

# **REFERENCES**

- [1] Shahid, H. (2024, February 1). *How chiplets are revolutionizing China's semiconductor industry*. The Korea Times. https://www.koreatimes.co.kr/www/opinion/2024/01/137\_355297.html

- [2] Cadence. (2023). *The rise of chiplets*. PCB Design & Analysis. https://resources.pcb.cadence.com/blog/2023-the-rise-of-chiplets

- [3] The Economic Times. (2023). *Chip wars: How chiplets are emerging as a core part of China's tech strategy*. <a href="https://economictimes.indiatimes.com/tech/technology/chip-wars-how-chiplets-are-emerging-as-a-core-part-of-chinas-tech-strategy/articleshow/101723403">https://economictimes.indiatimes.com/tech/technology/chip-wars-how-chiplets-are-emerging-as-a-core-part-of-chinas-tech-strategy/articleshow/101723403</a>

- [4] IBM Research. (n.d.). What are chiplets? https://research.ibm.com/blog/what-are-computer-chiplets

- [5] ChipEdge. (n.d.). *Power of chiplets in the semiconductor industry*. <a href="https://chipedge.com/power-of-chiplets-in-the-semiconductor-industry/">https://chipedge.com/power-of-chiplets-in-the-semiconductor-industry/</a>

- [6] Kandou. (2023, September 18). *History of the chiplet and why it is the future*. https://www.kandou.com/glasswing/2023-09-18-history-of-the-chiplet-and-why-it-is-the-future

- [7] Khanikar, Tulika, Jyoti Sheoran, and Vinod Kumar Singh. "Polymer clad silica fiber for refractive index sensing application." 2018 3rd International Conference on Microwave and Photonics (ICMAP). IEEE, 2018.

- [8] Li, T., Hou, J., Yan, J., Liu, R., Yang, H., & Sun, Z. (2020). Chiplet heterogeneous integration technology—Status and challenges. *Electronics*, 9(4), 670. <a href="https://doi.org/10.3390/electronics9040670">https://doi.org/10.3390/electronics9040670</a>

- [9] Pradeep's Tech Points. (n.d.). Chiplets. https://pradeepstechpoints.wordpress.com/category/chiplets/

- [10] Wang, X., Su, J., Chen, D., Li, D., Li, G., & Yang, Y. (2023). Efficient thermal-stress coupling design of chiplet-based system with coaxial TSV array. *Micromachines*, 14(8), 1493. https://doi.org/10.3390/mi14081493

- [11] Graening, A., Pal, S., & Gupta, P. (2023, July). Chiplets: How small is too small? In 2023 60th ACM/IEEE Design Automation Conference (DAC) (pp. 1–6). IEEE. <a href="https://nanocad.ee.ucla.edu/wp-content/papercitedata/pdf/c124.pdf">https://nanocad.ee.ucla.edu/wp-content/papercitedata/pdf/c124.pdf</a>

- [12] Zhuang, Z., Yu, B., Chao, K. Y., & Ho, T. Y. (2022, October). Multi-package co-design for chiplet integration. In *Proceedings of the 41st IEEE/ACM International Conference on Computer-Aided Design* (pp. 1–9). https://www.cse.cuhk.edu.hk/~byu/papers/C147-ICCAD2022-MPCD.pdf

- [13] Han, Y., Xu, H., Lu, M., Wang, H., Huang, J., Wang, Y., ... & Sun, N. (2023). The big chip: Challenge, model and architecture. *Fundamental Research*. https://doi.org/10.1016/j.fmre.2023.10.020

- [14] Yang, Z., Ji, S., Chen, X., Zhuang, J., Zhang, W., Jani, D., & Zhou, P. (2023). Challenges and opportunities to enable large-scale computing via heterogeneous chiplets. *arXiv preprint arXiv:2311.16417*. https://arxiv.org/pdf/2311.16417.pdf

- [15] Boston Consulting Group (BCG). (2023, June). The future of automotive compute: Are chiplet systems a promising technology step on the path toward a centralized stack? <a href="https://media-publications.bcg.com/The-Future-of-Automotive-Compute.pdf">https://media-publications.bcg.com/The-Future-of-Automotive-Compute.pdf</a>

- [16] PCBAAA. (n.d.). Chiplet technology. https://www.pcbaaa.com/chiplet-technology/

- [17] BCG on Tech. (n.d.). *Chiplets: Opportunities and challenges for the semiconductor industry*. https://medium.com/bcgontech/chiplets-opportunities-and-challenges-for-the-semiconductor-industry

- [18] Loh, G. H., Naffziger, S., & Lepak, K. (2021, February). Understanding chiplets today to anticipate future integration opportunities and limits. *Advanced Micro Devices Inc.* https://past.dateconference.com/proceedings-archive/2021/pdf/2001.pdf

- [19] Cadence. (2023). *The rise of chiplets*. PCB Design & Analysis. https://resources.pcb.cadence.com/blog/2023-the-rise-of-chiplets

- [20] EE Times. (n.d.). Chiplets: A short history. https://www.eetimes.com/chiplets-a-short-history/

- [21] SEMI Taiwan. (n.d.). Chiplets at SEMICON Taiwan. https://www.semicontaiwan.org/en/node/7601

- [22] Semiconductor Engineering. (n.d.). Edge AI and chiplets. https://semiengineering.com/edge-ai-and-chiplets/