The Evolution of Interconnects in Microelectronics Packaging

By Dr. Dongkai Shangguan

3DIncites (November 14, 2024)

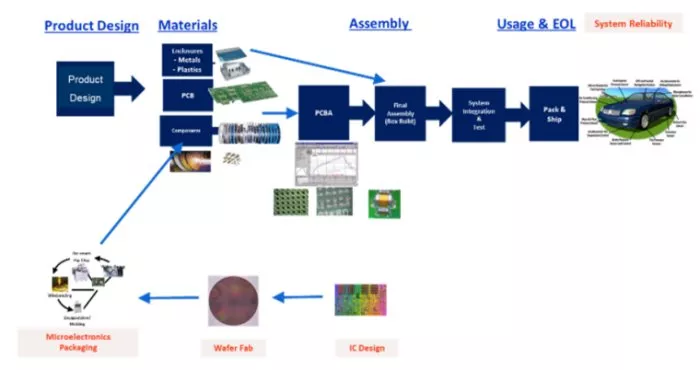

Semiconductor packaging is a complex and evolving field, involving multiple disciplines. As a microelectronics packaging engineer, I focus on the “interconnect thread” from the chip to the system (Figure 1).

To me, packaging is about interconnectivity (essentially). The primary function of packaging is to provide the interconnection from the IC to the system, for signal distribution and power distribution. What makes it more complex (and thus interesting) is the enabling functions, including mechanical reliability (especially under complex loading conditions in diverse use environments – thus various failure modes and mechanisms); thermal dissipation (especially important for high power and also due to the multiple interfaces in the system); as well as manufacturability that has to be considered (such as low temperature soldering, fine pitch processes, cost and quality, and very importantly, sustainability). These electro-mechano-thermal functions of the interconnect are what makes “packaging” such a critical area for semiconductor technology today. In the age of heterogeneous integration, a variety of interconnects in the same package have to be considered.

To read the full article, click here

Related Chiplet

- 12nm EURYTION RFK1 - UCIe SP based Ka-Ku Band Chiplet Transceiver

- Interconnect Chiplet

- Bridglets

- Automotive AI Accelerator

- Direct Chiplet Interface

Related News

- 2024 IEEE Electronic Components and Technology Conference to Spotlight Cutting-Edge Microelectronics Packaging Technologies; Photonic Devices, Heterogeneous Integration are Among Key Topics

- How the Worlds of Chiplets and Packaging Intertwine

- SKC invests in Chipletz, a rising star of the U.S. chip packaging industry

- CHIPS for America Releases Vision for Approximately $3 Billion National Advanced Packaging Manufacturing Program

Latest News

- Untether AI Enters Into a Strategic Agreement with AMD

- Alphawave Semi Tapes Out Breakthrough 36G UCIe™ IP on TSMC 2nm, Unlocking Foundational AI Platform IP on Nanosheet Processes

- How Secure Are Analog Circuits?

- Sarcina Technology advances photonic package design to address key data center challenges

- Imec demonstrates 16nm pitch Ru lines with record-low resistance obtained using a semi-damascene integration approach